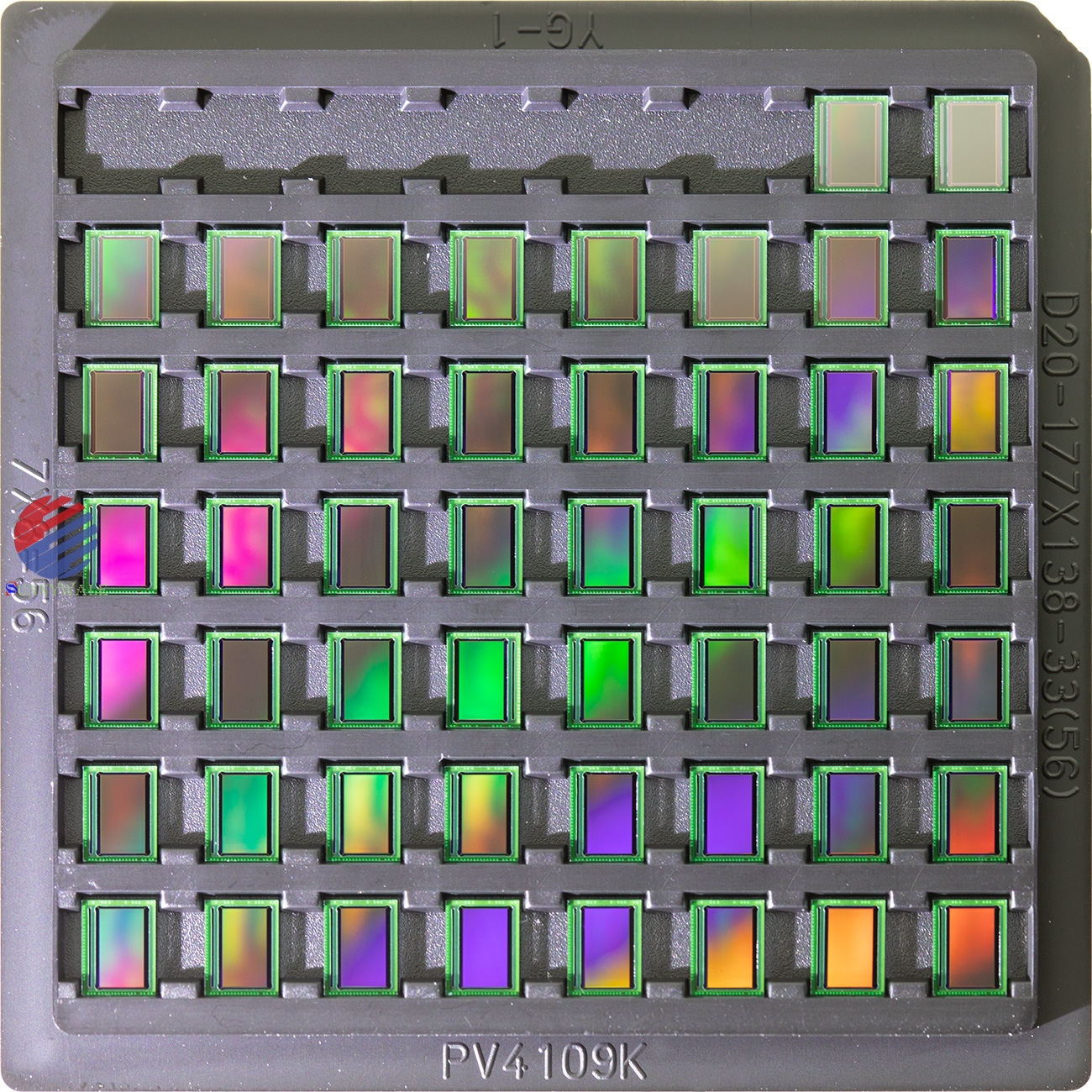

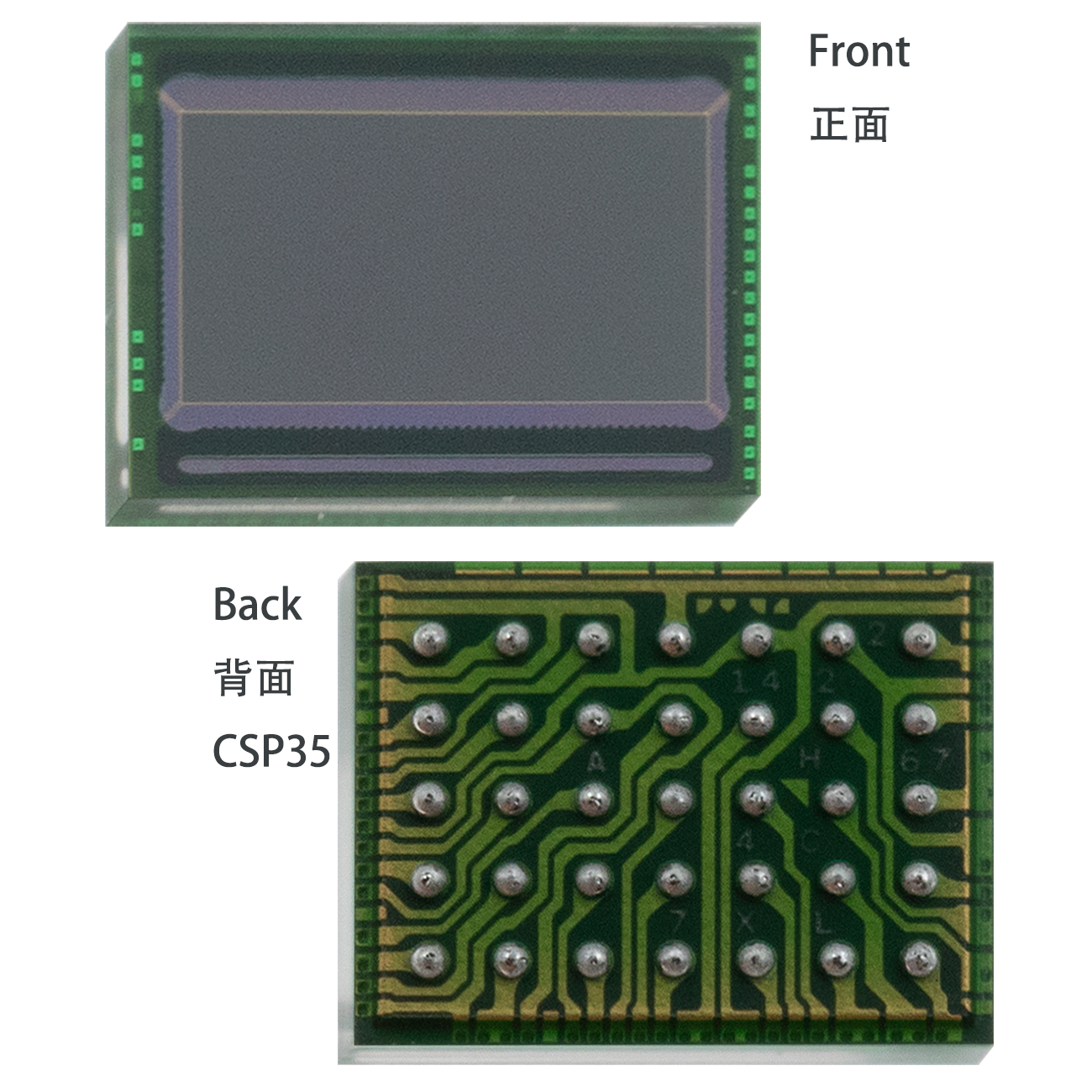

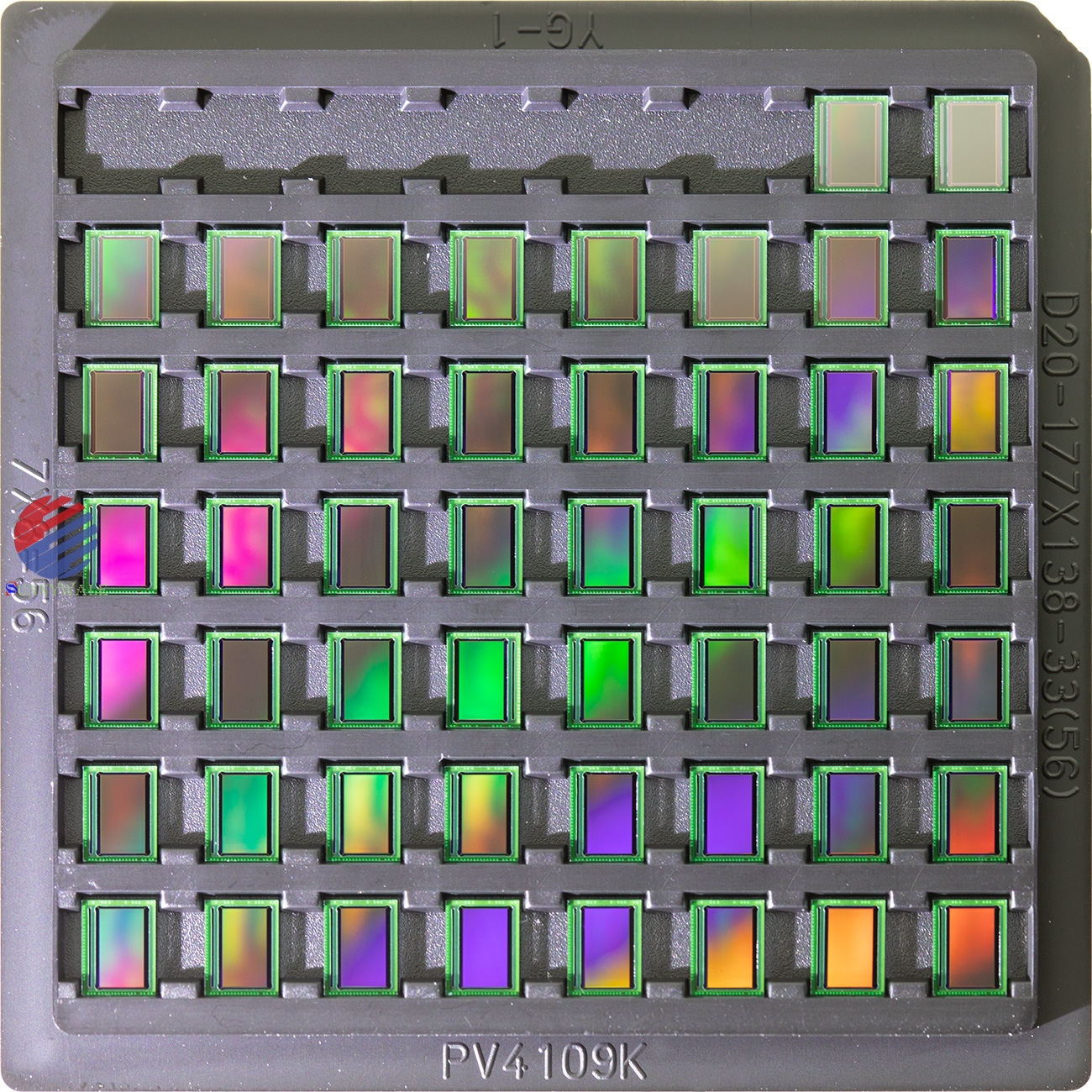

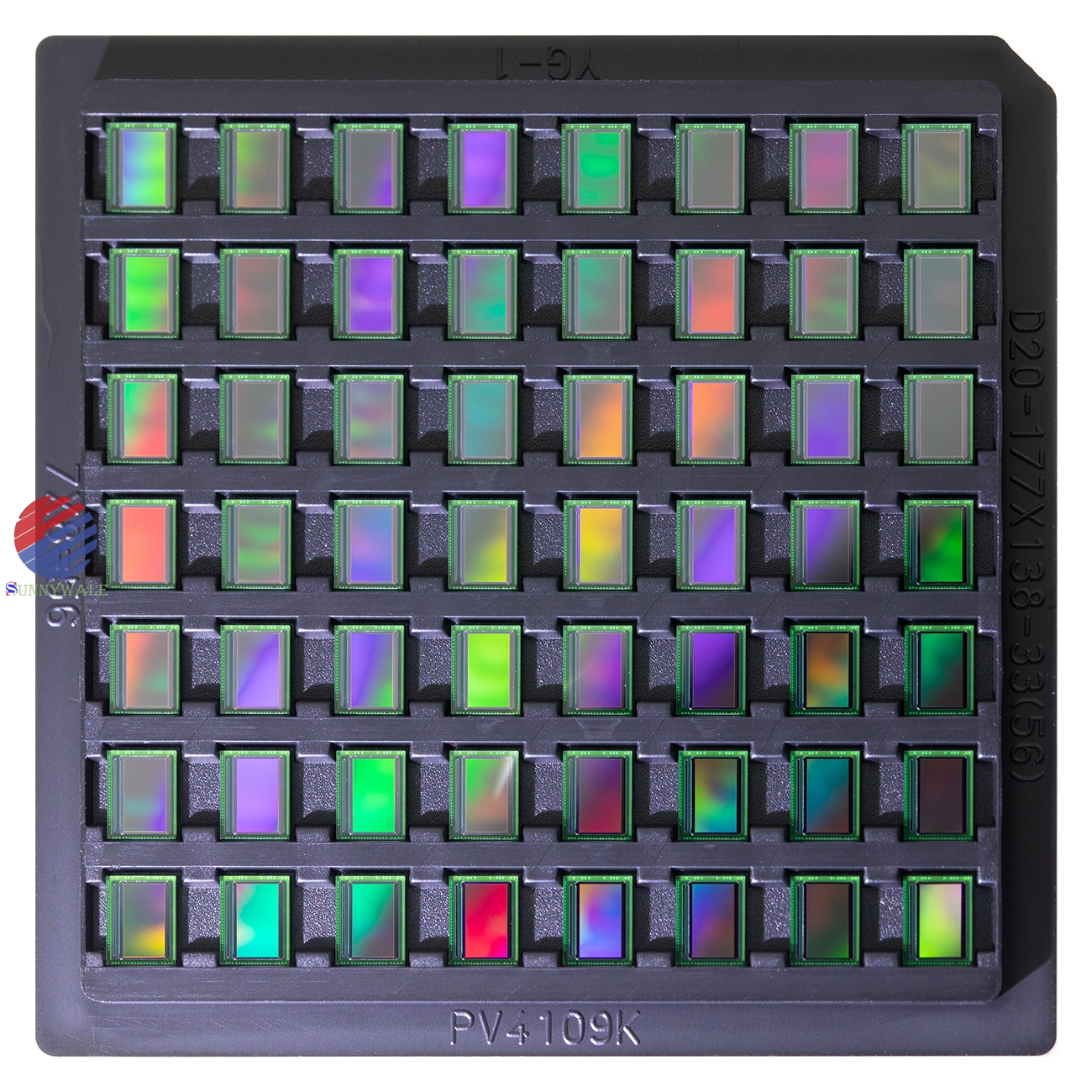

PV4109K, PIXELPLUS CMOS, CSP 1/4-inch sensor, HD Single Chip CMOS Image Sensor, with HD-Analog Transmitter cmos sensor, 1024X768@30fps analog sensor, DVP(Digital Video parallel) and HD-Analog interfac

2022-08-24 01:55:27

Buy Now

PV4109K, PIXELPLUS CMOS, CSP 1/4-inch sensor, HD Single Chip CMOS Image Sensor, with HD-Analog Transmitter cmos sensor, 1024X768@30fps analog sensor, DVP(Digital Video parallel) and HD-Analog interface output image sensor

PV4109K, PIXELPLUS CMOS, CSP 1/4-inch Ssensor, HD Single Chip CMOS Image Sensor, with HD-Analog Transmitter cmos sensor, 1024X768@30fps analog sensor, DVP(Digital Video parallel) and HD-Analog interface output image sensor

Features

● 1284x724 effective pixel array with RGB bayer color filters and micro-lens

● Output Interface

⊕ DVP(Digital Video Parallel) 8-bit

◎ Raw RGB Bayer 8-bit

◎ YCbCr422 8-bit

⊕ HD-Analog

● Auto black level compensation

● Programmable frame size, frame rate, window size, exposure and white balance gain

● Horizontal/Vertical mirroring

● Image processing on chip : lens shading compensation, gamma correction, defect correction, color correction, NR(2D noise reduction), color interpolation, edge enhancement, brightness, contrast, de-color, auto white balance, auto exposure control, back light compensation, Color saturation, Low light enhancement

● Automatic flicker cancellation

● Auto IR-LED/TDN(moving) filter controller with CdS

● Programmable static parking guideline

● Software reset

● On-chip phase locked loop ( PLL )

● I2C master included

● Crystal input support

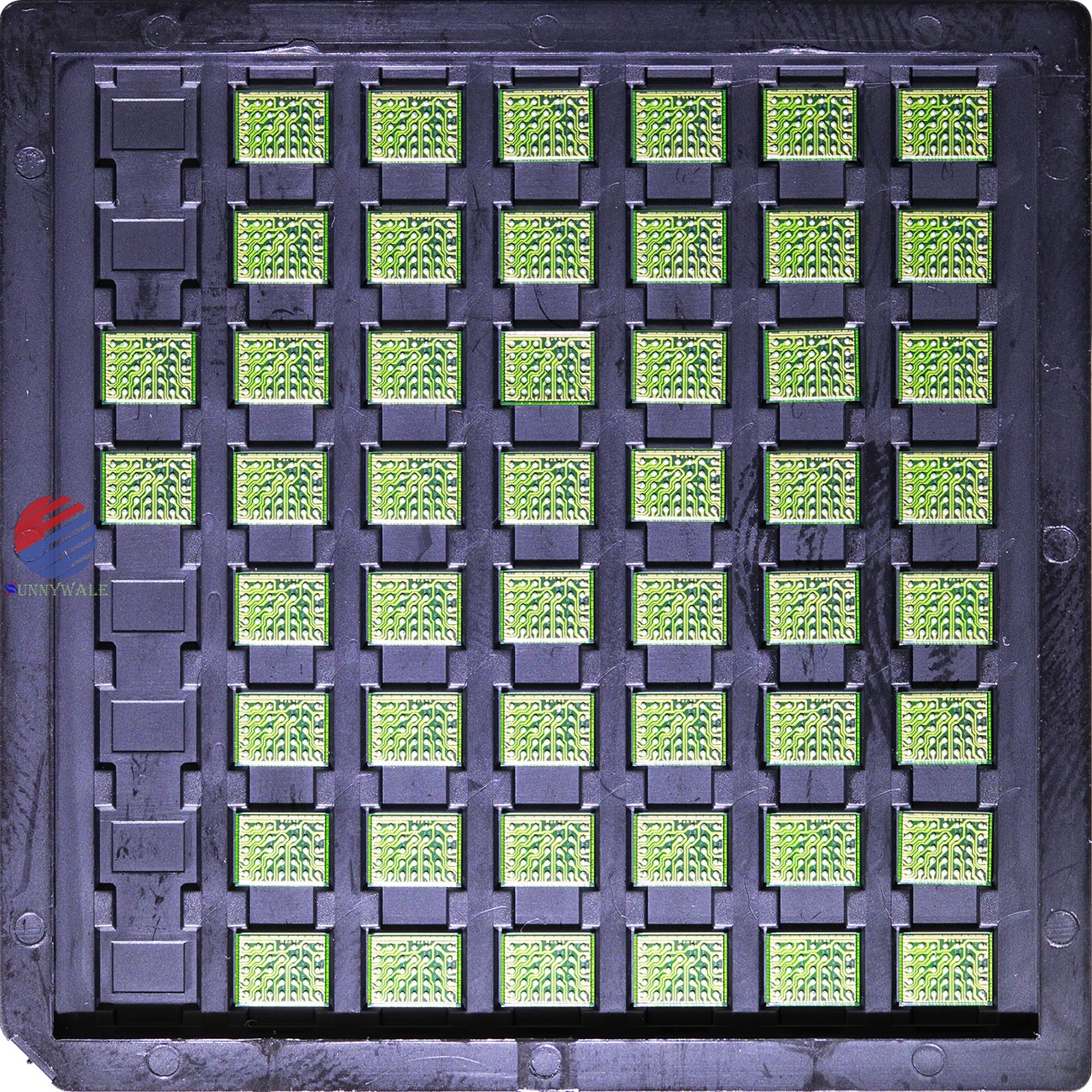

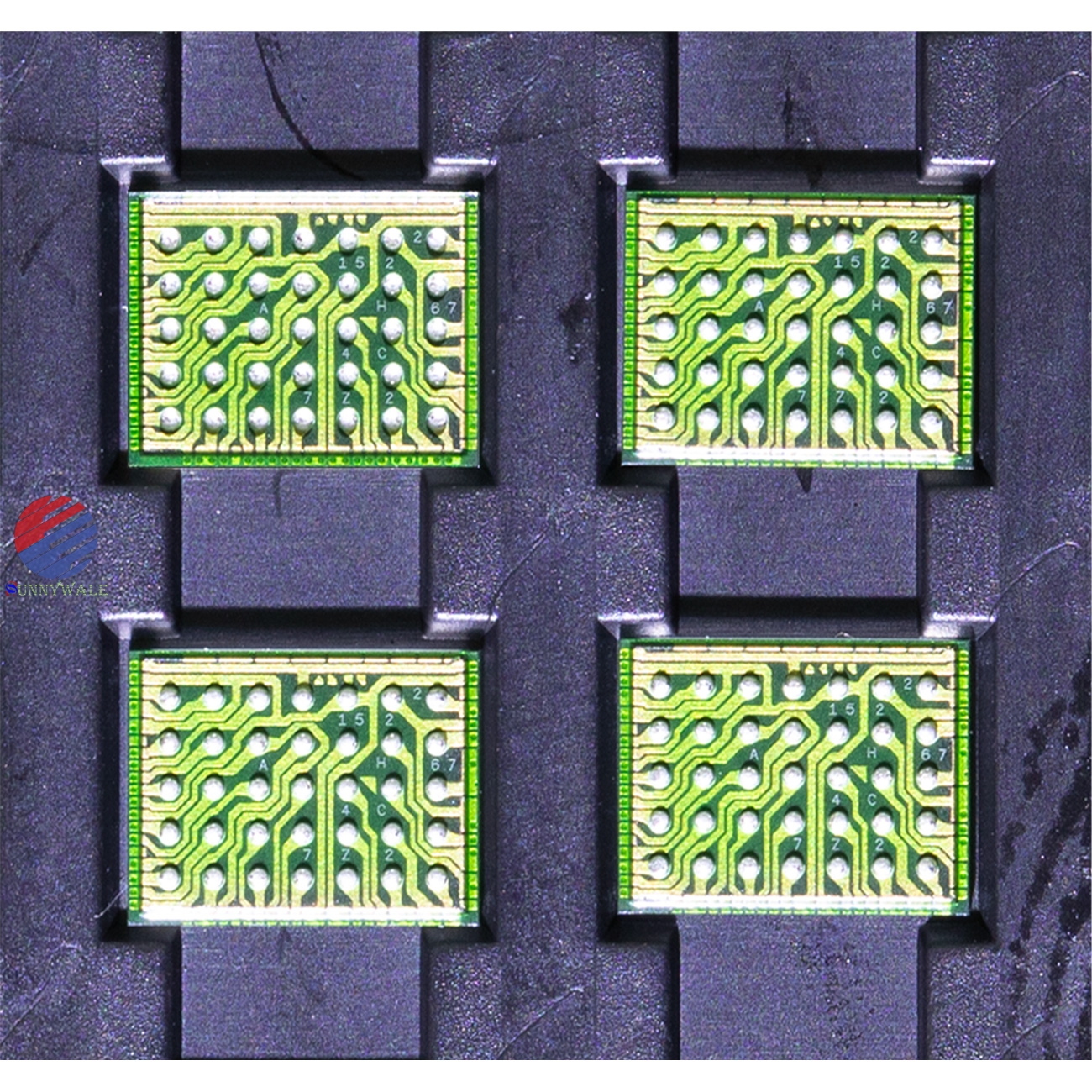

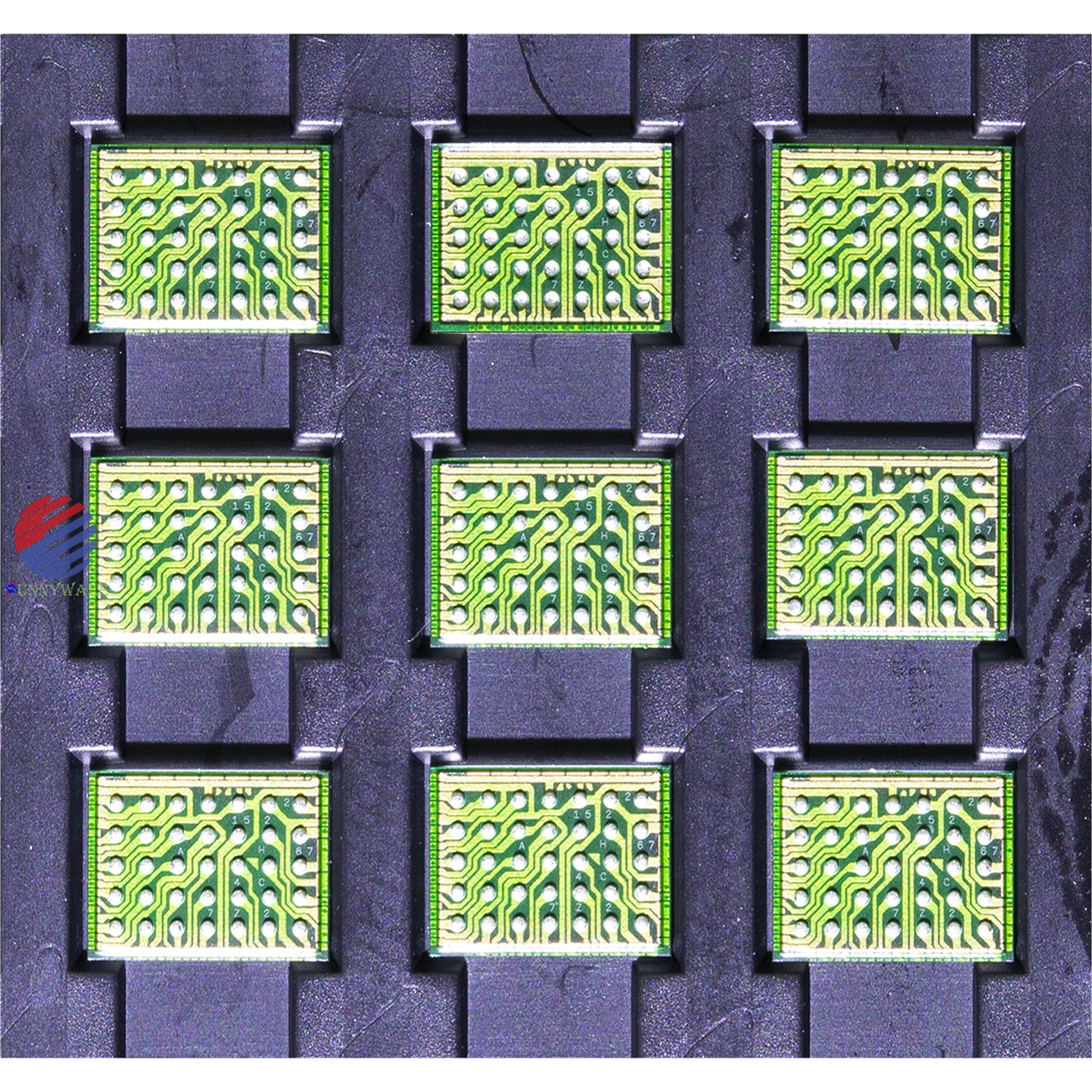

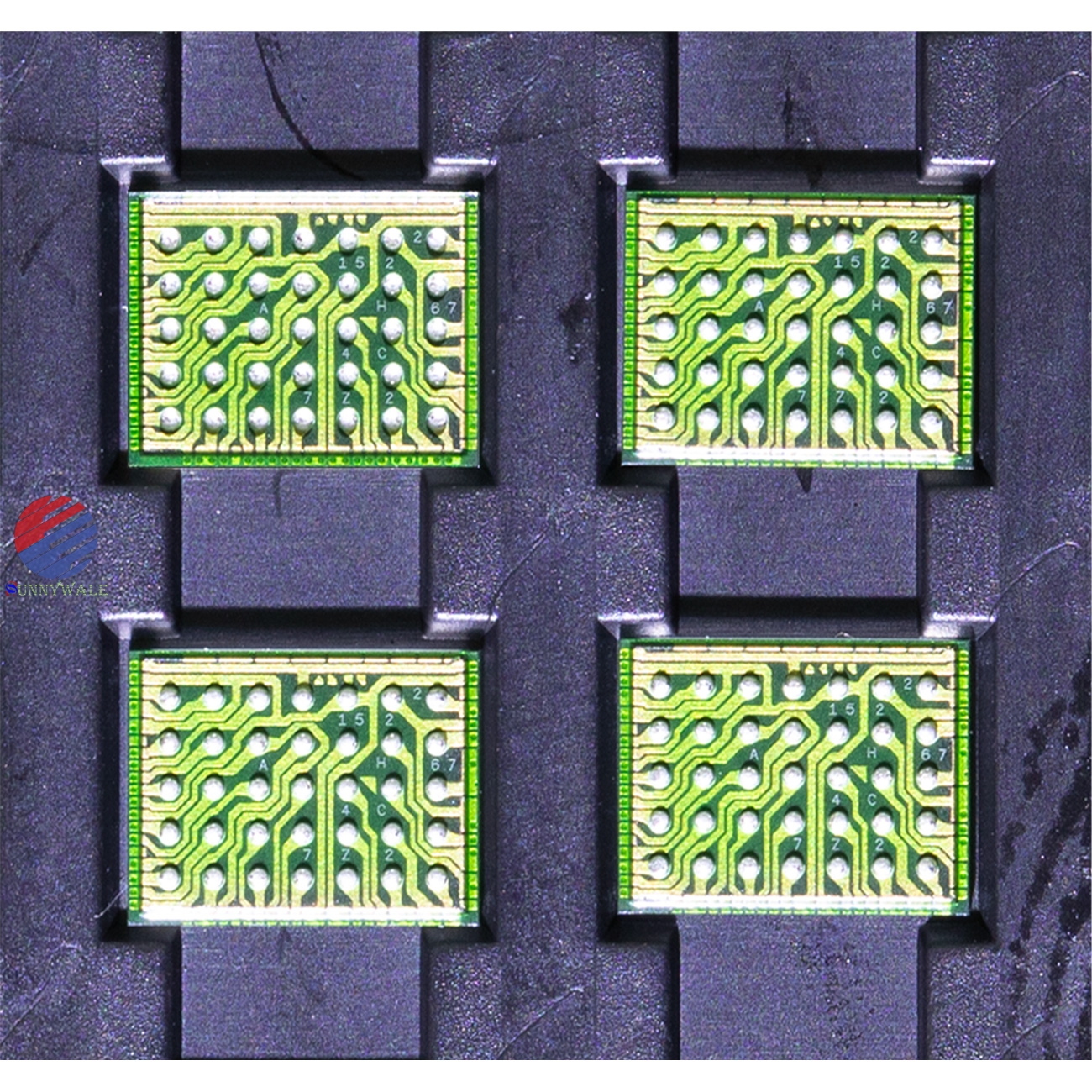

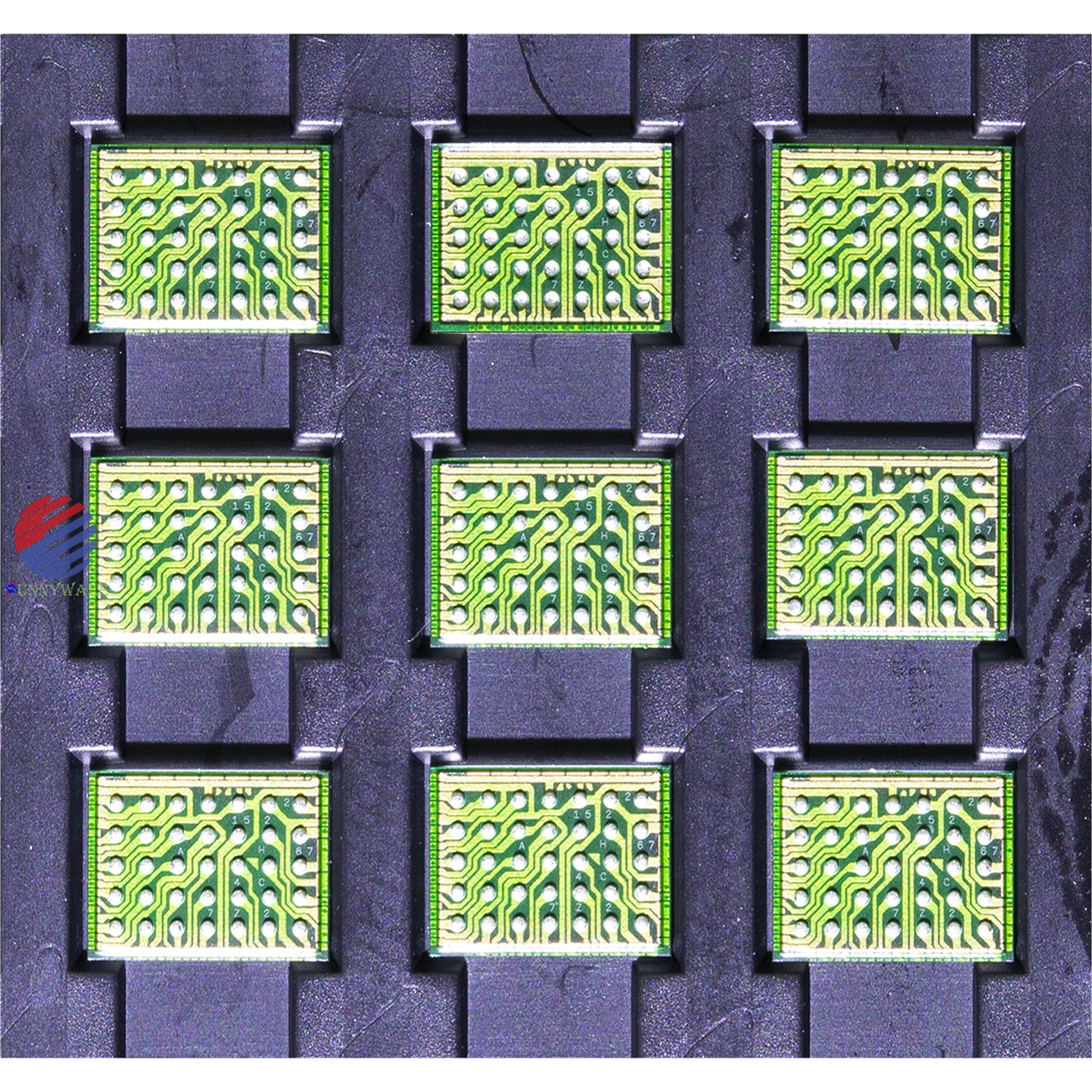

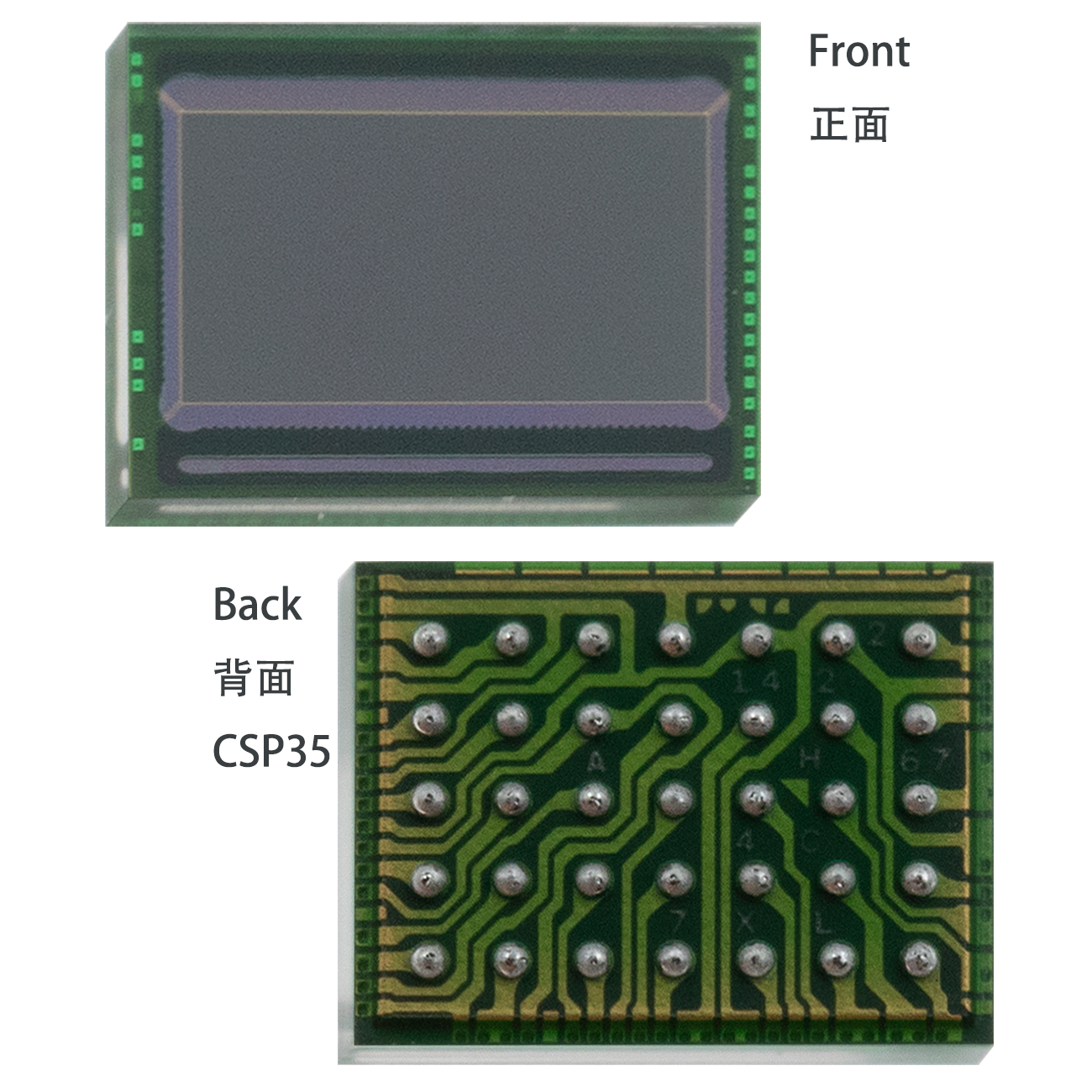

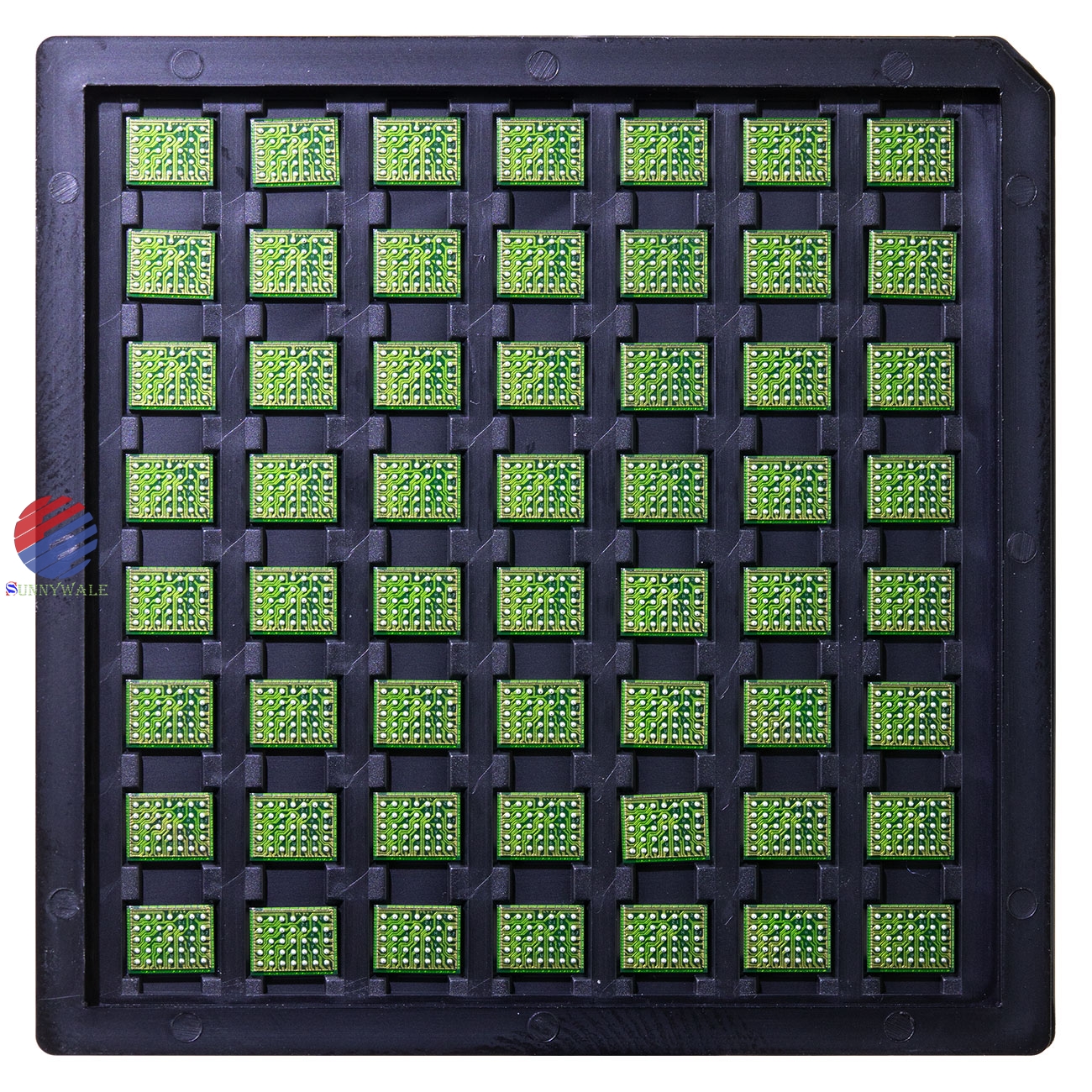

● Package :35Pin-CSP

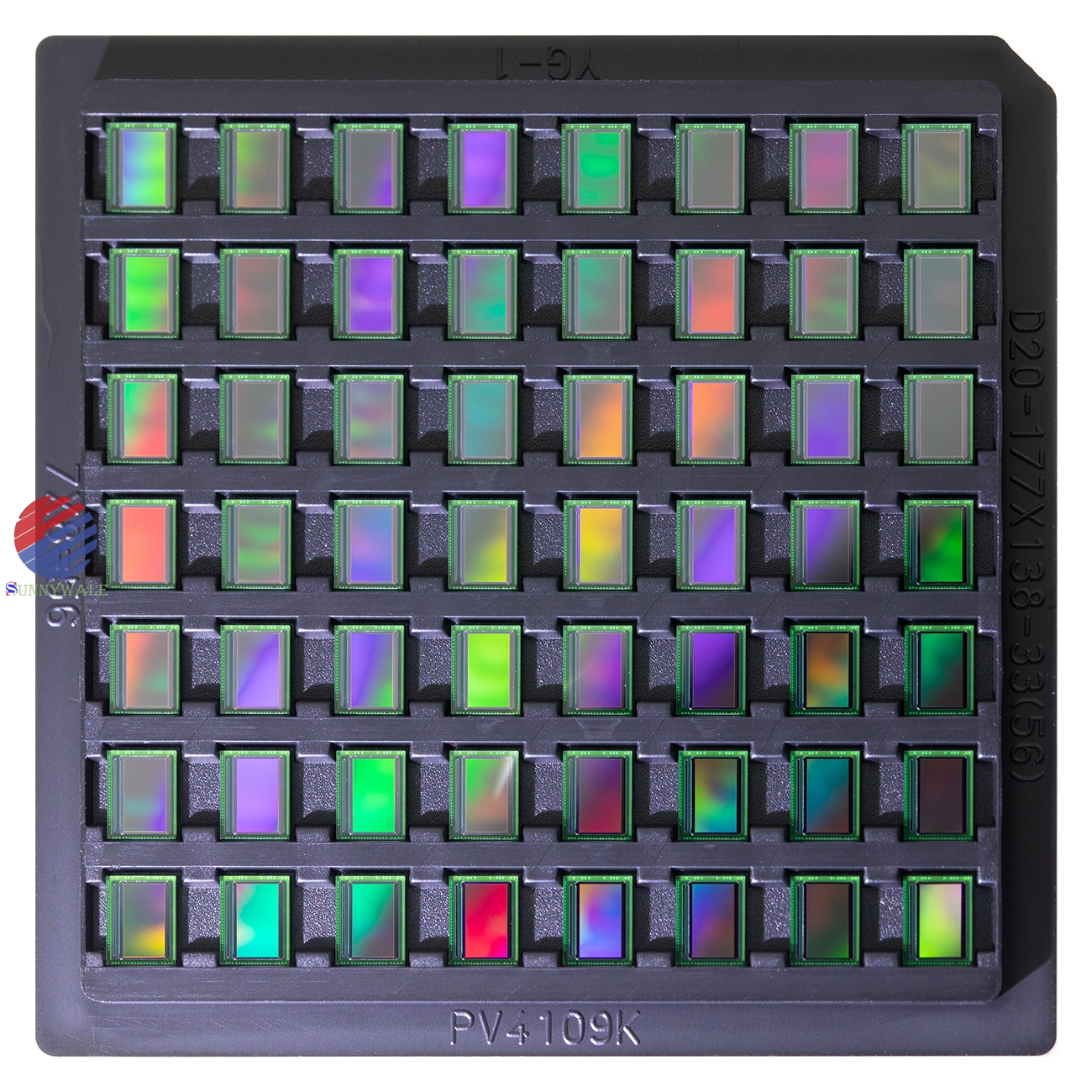

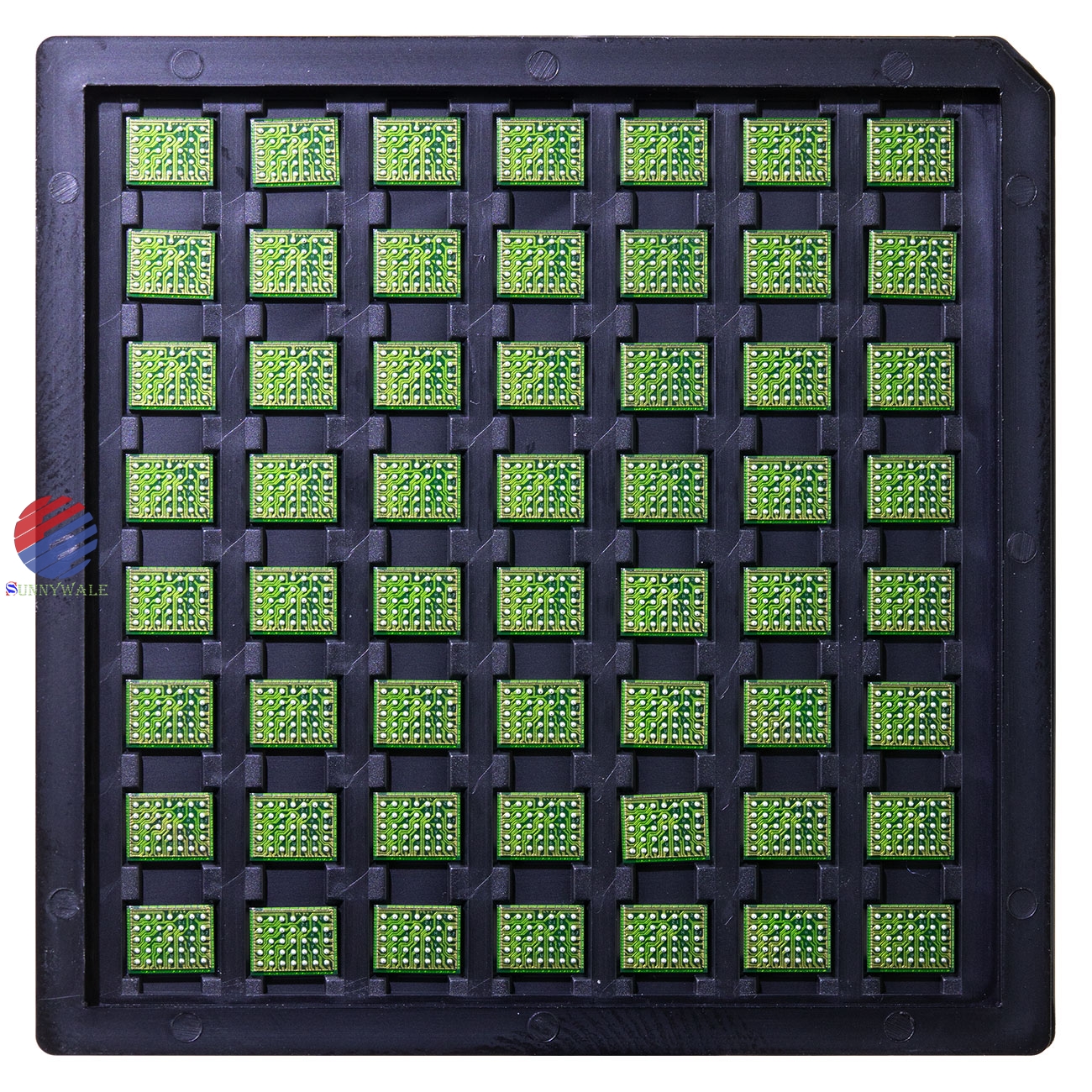

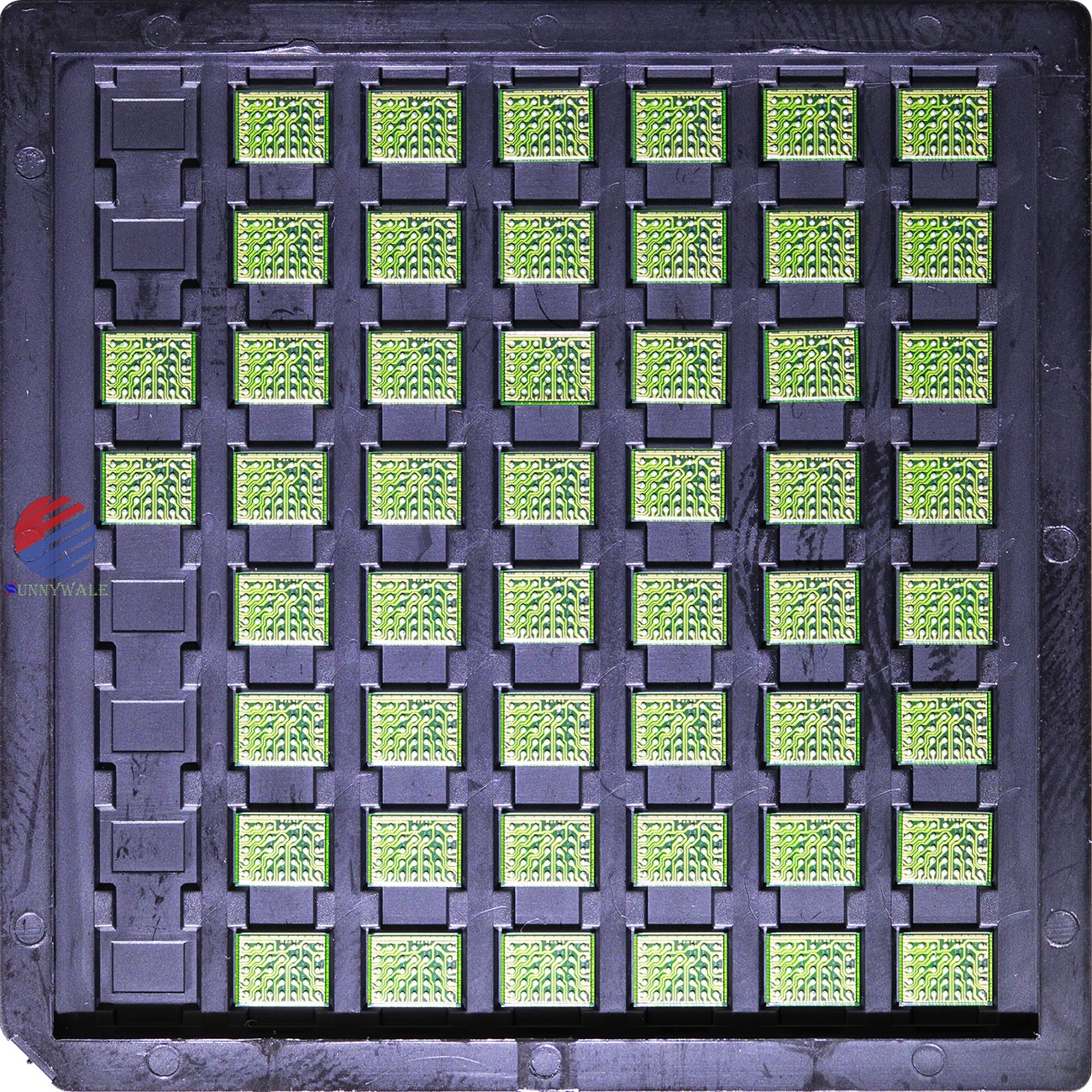

Note: ORIGINAL goods PV4109K are batch number unity (back word unity), non-original goods can not do this, this alone is enough to prove that this is the original goods, anyone in this respect have no ability to cheat.

Note: ORIGINAL goods PV4109K are batch number unity (back word unity), non-original goods can not do this, this alone is enough to prove that this is the original goods, anyone in this respect have no ability to cheat.

General Description

The PV4109K is a 1/4-inch CMOS image sensor with HD-Analog Transmitter. It is a single chip with an effective pixel array of 1284 (width) x 724 (height). The PV4109K can generate a PVI(HD-Analog) data at maximum frame rate of 30 FPS. On-chip sensor functions can be controlled through I2C interface.

Chip Architecture

The PV4109K has a 1284 x 724 total pixel array and includes column/row driver circuits for reading out pixel data progressively. CDS circuit reduces noises generated from various sources, which mainly are resulted from process variations. The fixed error signal level caused by pixel process variation can be reduced by sampling the difference between the output and the reset level of the pixel. Each of R, G, and B pixel output can be multiplied by different gain factors to balance the color of images under various light conditions. The analog signals are converted into digital data of one line at a time and each line data is streamed out column by column. The Bayer RGB data passes through a sequence of image signal processing to produce various output datas. Image signal processing includes operations such as gamma correction, defect correction, low pass filter, color interpolation, edge enhancement, color correction, contrast stretch, color saturation, white balance, exposure control and back light compensation. The PV4109K with PVI TX supports PVI(HD-Analog) analog output. The

control of internal functions and output signal timings can be enabled by modifying registers directly through a 2-wire serial interface called I2C or by programming the internal/external ROMs which contain device settings.

Frame Structure

The size of a frame is determined by framewidth and frameheight registers. One frame consists of (framewidth+1) columns and (frameheight+1) rows, where the size of one frame is allowed to be larger than the total pixel array size. Window determines the output image size, and its default size is 1280 x 720 pixels. It is possible to define a specific region of the frame by a determined window. Pixel scanning is performed row by row on entire frame. Frame row counter and frame column counter, which are limited by framewidth and frameheight values respectively, are used to indicate the current coordinate of pixel being scanning. The column counter value increase by every pixel clock (pclk). every time the column counter reaches maximum value, the row counter value increase. Figure 2 shows the default frame structure and the window position of the PV4109K with origin point (0,0) in the top right corner.

PV4109K datasheet PDF file可免费下载,Click or copy the link to free download the datasheet PDF file.

Freight is free when you buy 2 pieces in China, if you have PV4109K inventory, you can sell to me, if you need buyPV4109K, you can ask me to buy.

If you want to know about similar products **, or click here,or Visit The official website: sunnywale.com,Search the keywods“

PIXELPLUS”,it can show more details.

If you are not used to reading English, you can watch the

中文 version