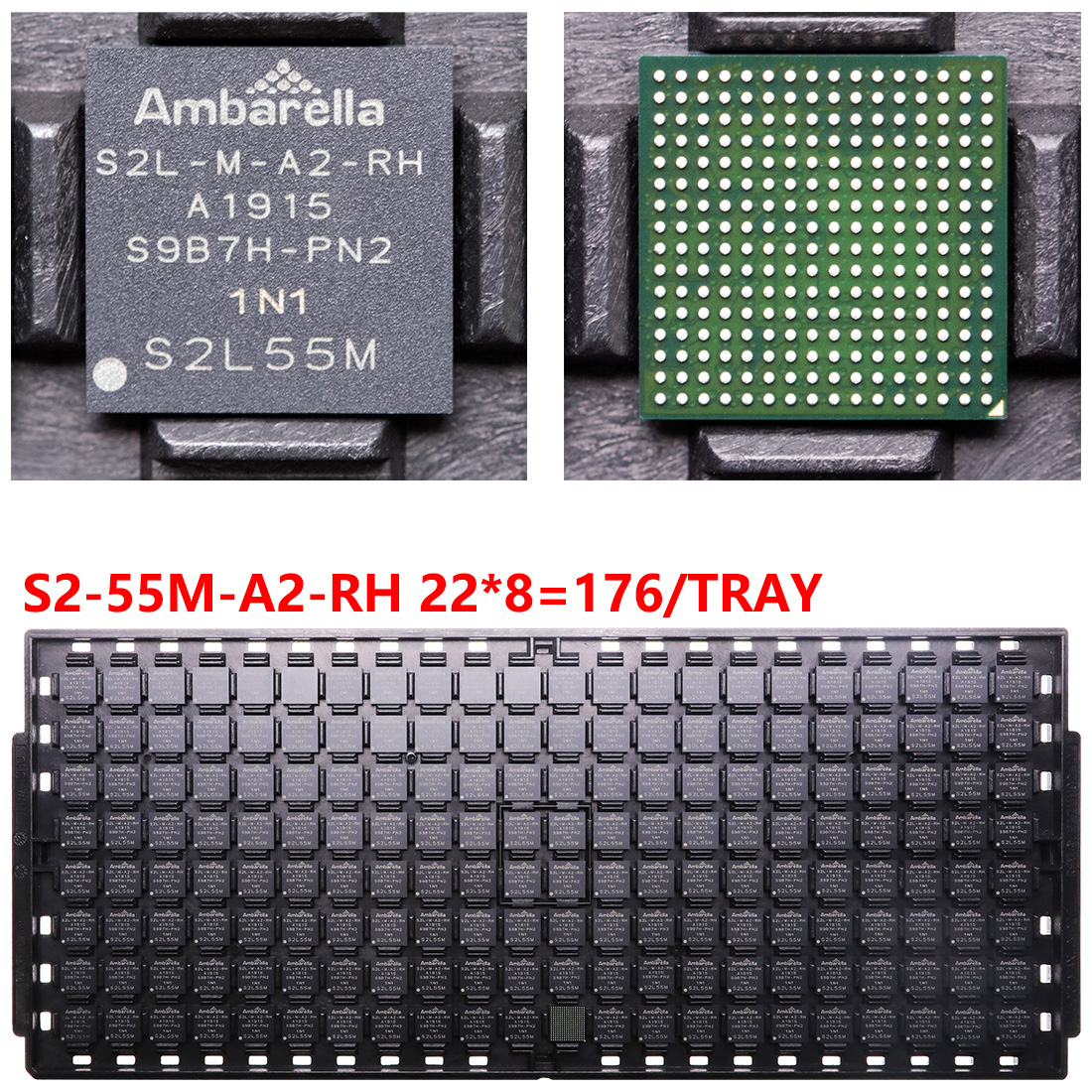

S2L55M Ambarella integrated system chip platform SoC for advanced network IP CAMERA,600Mhz ARM Cortex-A9 architecture CPU and a high performance digital signal processing (DSP) subsystem, image sensor

2021-06-29 20:56:44

Buy Now

SUMMARY DESCRIPTION

The S2L55M is an integrated system-on-achip (SoC) platform that targets IP cameras for advanced consumer/cloud 3Mp30 surveillance applications with HDR support.

S2L55m chips provide a 600-MHz ARM Cortex-A9 CPU and a high-performance digital signal processing (DSP) subsystem with an image sensor pipeline (ISP) and a high-definition (HD) H.264 codec engine.

KEY FEATURES

※ Embedded ARM Cortex-A9 600-MHz CPU with L2 cache

※ More than 240 MPixel/s processing rate

◎ 5-MPixel maximum sensor resolutior

※ Lens distortion correction for wide-angle lenses

※ Wide Dynamic Range (WDR) image processing

※ High Dynamic Range (HDR) engine with multiexposure fusion

※ 3D noise reduction (Motion Compensated Temooral Filter, or MCTF)

※ Н.264 BP/MP/HP Level 4.1 and MJPEG codecs

※ Maximum encode resolution: 5 Mpixels

※ Support for Ambarella SmartAVC low bitrate streaming

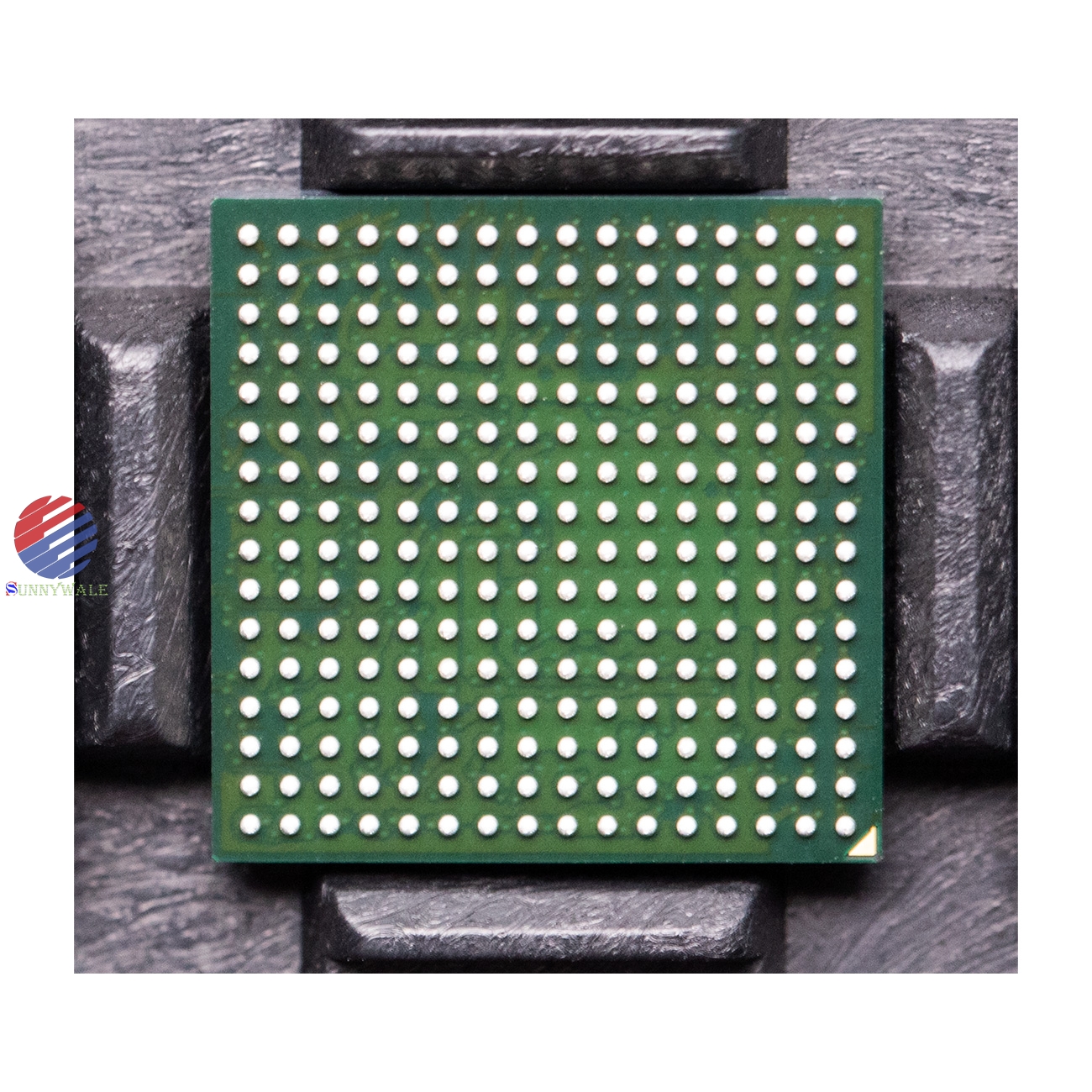

※ 256-pin, 0.65-pitch TFBGA package (11 mm x 11 mm)

※ 28-nm CMOS Low Power (LP) technology

※ Operating temperature from 0℃ to 70 ℃

1. OVERVIEW

This preliminary datasheet for the S2L55M processor from Ambarella begins with a brief introduction to the chip (Section 1.1) and a summary of key features (Section 1.2). Chapter 2 describes the S2L55m peripheral interfaces. For pin details and electrical characteristics refer to Chapter 3 and Chapter 4, respectively. See Chapter 5 for package information and Chapter 6 for Ambarella contact and ordering details.

Please note that the chip features described in this datasheet are subject to change. Details that have not been entirely finalized (e.g., encoding specifics) are provided using conservative estimates (i.e., final encoding performance is expected to meet or exceed the estimate provided).

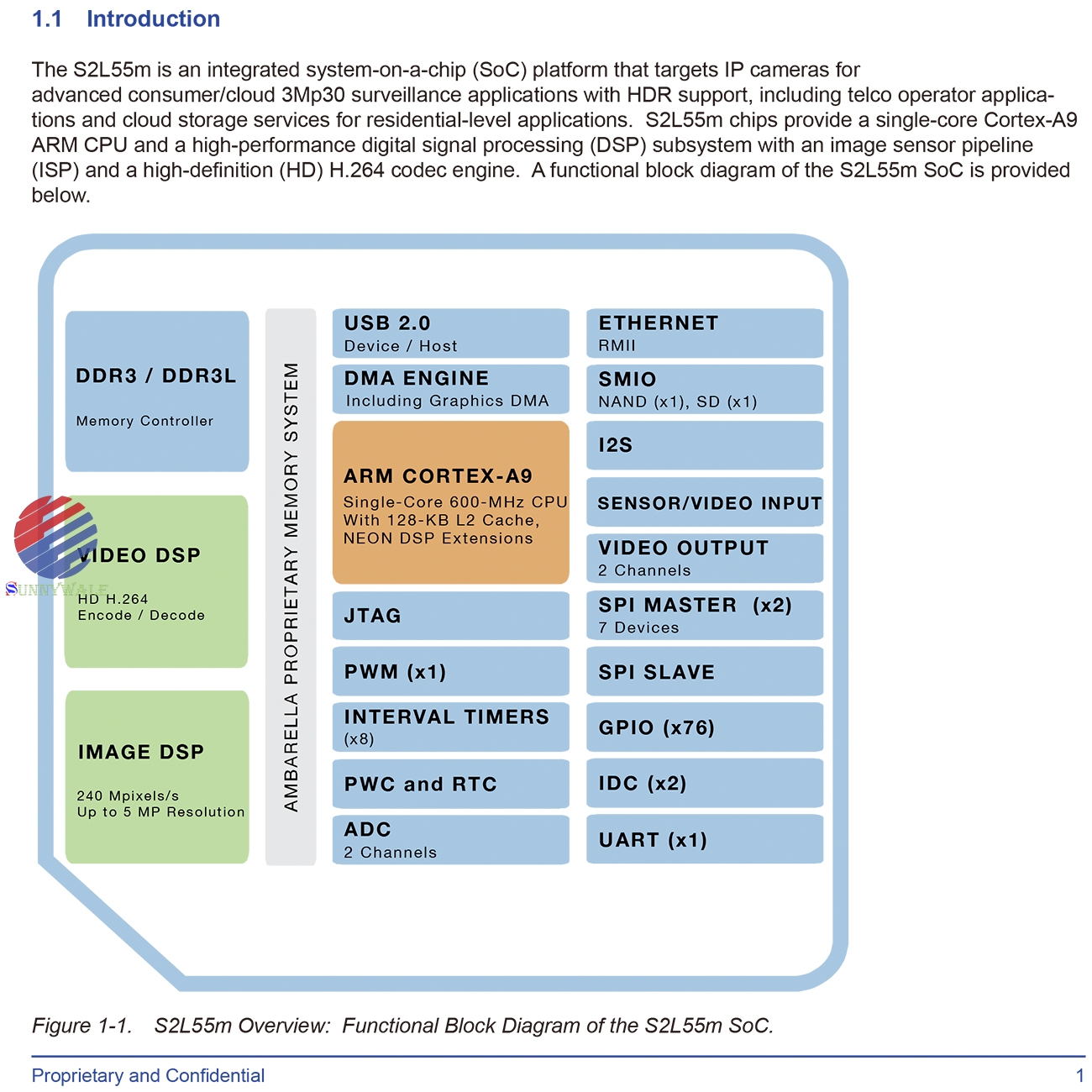

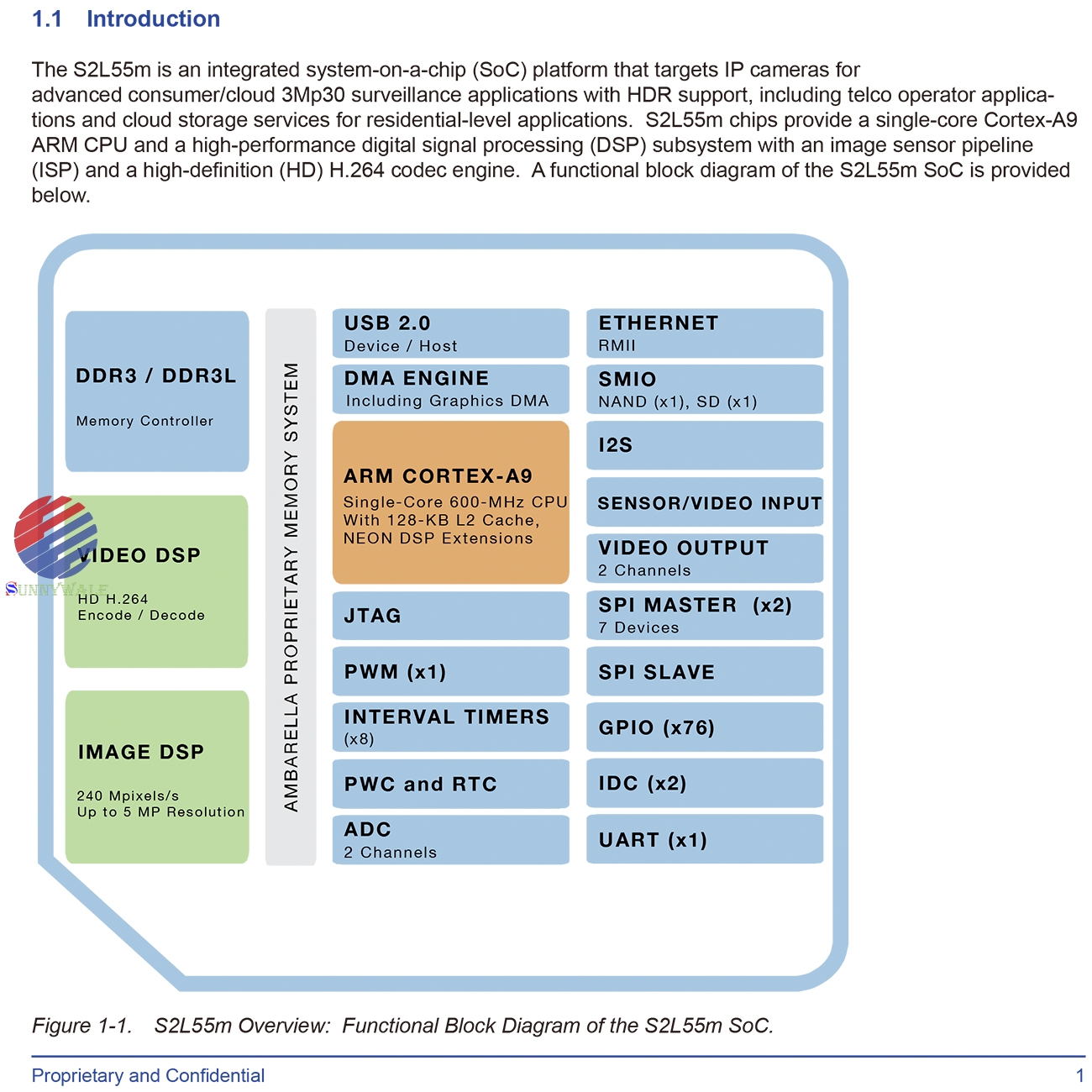

1.1 Introduction

The S2L55M is an integrated system-on-a-chip (SoC) platform that targets IP cameras foradvanced consumer/cloud 3Mp30 surveillance applications with HDR support, including telco operator applications and cloud storage services for residential-evel applications. S2L55m chips provide a single-core Cortex-A9 ARM CPU and a high-performance digital signal processing (DSP) subsystem with an image sensor pipeline (ISP) and a high-definition (HD) H.264 codec engine. A functional block diagram of the S2L55m SoC is provided below .

The S2L55M SoC provides a glueless interface to Serial SLVS. HiSPi, and MIPI interfaces, as well as paralle connections to popular CMOS image sensors. The ISP offers advanced image-processing features including improved high dynamic range (HDR) processing with multi-exposure fusion, wide dynamic range (WDR) singleexposure tone mapping with local contrast enhancement, 3D noise reduction (Motion Compensated Temporal Filter, or MCTF), and geometric lens correction (for wide-angle lenses).

The H.264 codec engine delivers versatile encoding up to 3Mp30 total performance, including up to four simul taneous encode streams and support for up to 5 MP H.264 and 5 MP JPEG. The high-efficiency H.264 encoder supports SmartAVC, as well as advanced Main and High-Profile functions for the highest-quality and lowest possible bitrate. These functions include bidirectional prediction (B-frames), large motion-estimation search range, and macroblock-level quantization. Ambarella builds in flexibility with a multi-streaming function (up to four streams), allowing on-the-fly start/stop as well as the adjustment of the bitrate, frame rate, and GOP of each individual stream

A 600-MHz ARM Cortex-A9 CPU with NEON DSP extensions and floating point support is available for implementing full-featured user applications.

The S2L family is fabricated using low-power 28-nm CMOS technology and integrates advanced power-saving modes, such as utilizing DSP-subsystem memory resources to reduce external memory bandwidth and total camera system power requirements. The S2L evaluation kit (EVK) and software development kit (SDK) provide a Linux-based framework and development environment that includes demonstration applications, source code image-tuning tools, and a rich set of APls that expose the DSP imaging and codec functionality at the ARM level enabling a range of product customization and differentiation options.

1.2 Feature List

Features of the S2L55m chip include:

※ Embedded ARM single-core Cortex-A9 CPU

◎ Clock frequency up to 600 MHz

◎ 32-KByte data/ 32-KByte instruction cache

◎ 128-KByte L2 cache

◎ NEON SIMD engine

◎ Floating Point Unit (FPU)AES/3/DES/SHA-1/MD5 encryption engine

※ DR3 and DDR3L controller

◎ Up to 528-MHz clock rate

◎ 16-bit wide data bus

◎ Maximum capacity of 2 Gbits (256 MBytes)

※ Image pipeline

◎ More than 240 MPixel/s processing rate

◎ 5-MPixel maximum sensor resolution

◎ Geometric lens correction (for wide-angle lenses)

◎ Black level correction

◎ Dynamic and static defect pixel cluster correction

◎ RGB Bayer demosaicing

◎ Lens shading correction

◎ 3D LUT color transform with gamma

◎ Wide Dynamic Range (WDR) single-exposure tone mapping

◎ High Dynamic Range (HDR) engine with multi-exposure fusion

◎ 3D noise reduction (Motion Compensated Temporal Filter, or MCTF)

◎ Flexible APls and image-tuning tools

◎ Adjustable 3A; exposure, white balance and focus control (AE/AWB/AF)

◎ RGB and YUV statistics, histogram and AF focus value generation

◎ Luma sharpen and chroma noise filter

◎ Four resizers (1/16x to 8192x scaling) with digital pan, tilt and zoom (PTZ)

◎ Crop, mirror, flip, 90°/270° rotation

◎ Alpha-blending OSD up to full-frame overlay for text, image and privacy mask

※ Video engine

◎ Maximum encode resolution: 2592x1944

◎ H.264 BP/MP/HP Level 4.1 and MJPEG codecs।

◎ Encode performance up to 3Mp30 with four flexible streams

- Up to four real-time simultaneous encodes with on-the-fly start/stop as well as the adjustment of the bitrate, frame rate, and GOP of each individual stream

◎ Advanced H.264 compression tools

- I, IP, IBP modes (M=1,2,3; IP, IBP, IBBP)

- SVCT Scalable Video Coding

◎ Flexible rate control

- SmartAVC ultra-low bitrate H.264 streaming

- CBR. VBR and Constant QP with max bitrate control

- Macroblock-level adaptive quantization

◎ Dynamic ROl encoding with unrestricted number of free-form areas at macroblock boundary

※ Sensor/Video Input (VIN) interface

◎ Multiple input modes

- Supports up to 8-lane SLVS/HiSPi input

- Supports up to 4-lane MIPI input

- Support for 14-bit parallel and LVCMOS sensors

◎ Support for popular CMOS sensors; Aptina, Sony, OV, Panasonic

◎ 16-bit CCIR.601 video input with external sync signals

◎ 8-bit, 10-bit, 12-bit or 14-bit BT.656 video input with embedded sync codes including full-data range support

※ Video Output (VOUT) interfaces

◎ Two video output ports

- One logical channel drives analog

- One logical channel drives digita

◎ Popular LCD panel controllers (RGB mode)

◎ Support for RGBA and YUVA OS

◎ DVideo DAC for 480i/576i composite PALNTSC output

◎ BT. 656 embedded sync YUV output (8-bit or 16-bit mode)

※ AHB Bus DMA controller

◎ Memory-to-memory transfers including support for transfers between memory and peripherals

◎ Programmable transfer count up to 4 MB

◎ DMA scatterlaather via chained descriotor list in memory with DMA control information source

※ Dedicated DMA co-processor for graphics and image operations

◎ Offers linear copy, 2-D copy, composite, and alpha-blend image operations

◎ Supports 4- to 32-bit pixel formats

※ 12S digital audio interface (stereo)

◎ Audio record/playback

※ Ethernet MAC controller

◎ IEEE 802.3 compliant with full- and half-duplex(IEEE 802.3x low-control) and Jumbo frames

◎ IEEE 802.3xEEE 802.1Q VLAN tag detection

◎ Checksum offi-load for received IP and TCP/UDP packetshtrol) and Jumbo frames

◎ Dedicated pins for RMIl or MIll interface

◎ FIFO (2 KB /2 KB) and DMA support

※ One USB 2.0 interface

◎ One port configurable as host or device, with built-in PHY

※ Flexible Storage Media Input / Output (SMIO) interface

◎ NAND Flash controller

- Up to 8-Gbit device, 512-Byte and 2-KByte page sizes

- 8-bit flash chip data bus

- 4-bit and 8-bit SLC with ECC hardware and read-confirm support

- BCH error correction and increased spare area available

※ One SD controller (SDO)1

◎ bit, 4-bit SD modes, CRC7 for command and CRC16 for data integrity

※ Multiple boot options

◎ SPI-NOR, NAND Flash, USB and eMMC

※ Vector interrupt controller including VIC CPU-offload functionality

※ SSI/ SPI controller interfaces

◎ Two SSI/ SPI masters with up to seven device enables

◎ One dedicated SSI/ SPI slave port to connect to an external system master

※ Two-wire serial Inter-Integrated Circuit (IDC) interfaces (x2)

◎ Configurable IDC buses

※ UART interfaces (x2)

※ Up to 76 General Purpose Input/Output (GPIO) short-height pins with individual pull-up/down control

※ ADC (two channels) with high/low threshold interrupt generation and 12-bit resolution

※ Built-in power controller for power-up/down sequencing

※ Real Time Clock (RTC)

※ Interval timing with eight general-purpose timers confiqurable as external event counters

※ Watchdog timer (one)

※ One Pulse Width Modulator (PWM)

※ JTAG In-Circuit Emulator (ICE) interface for debugging (one)

※ 256-pin. 0.65-pitch TFBGA package (11 mm x 11 mm)

※ 28-nm CMOS Low Power (LP) technology

※ Operating temperature from 0 ℃ to 70 ℃