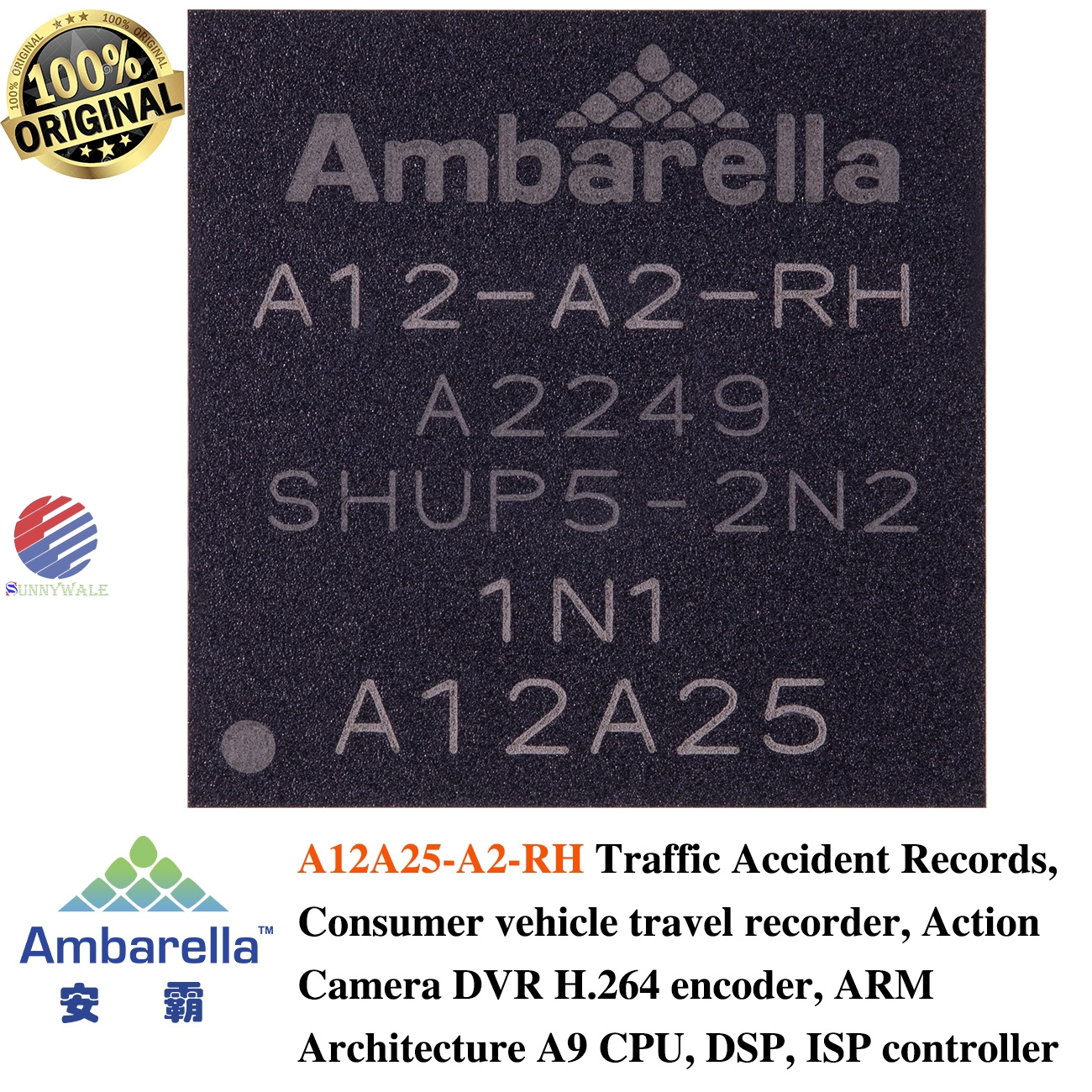

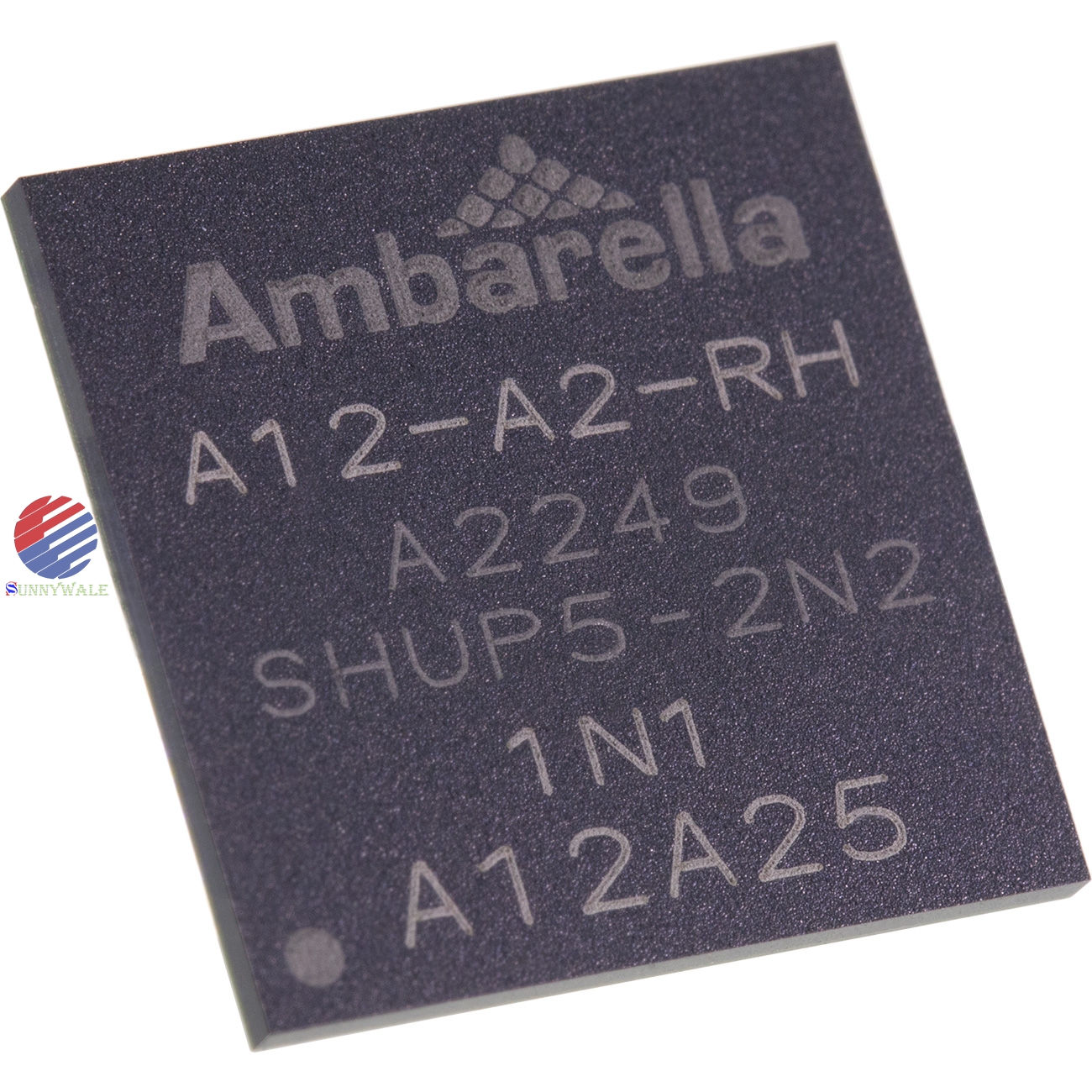

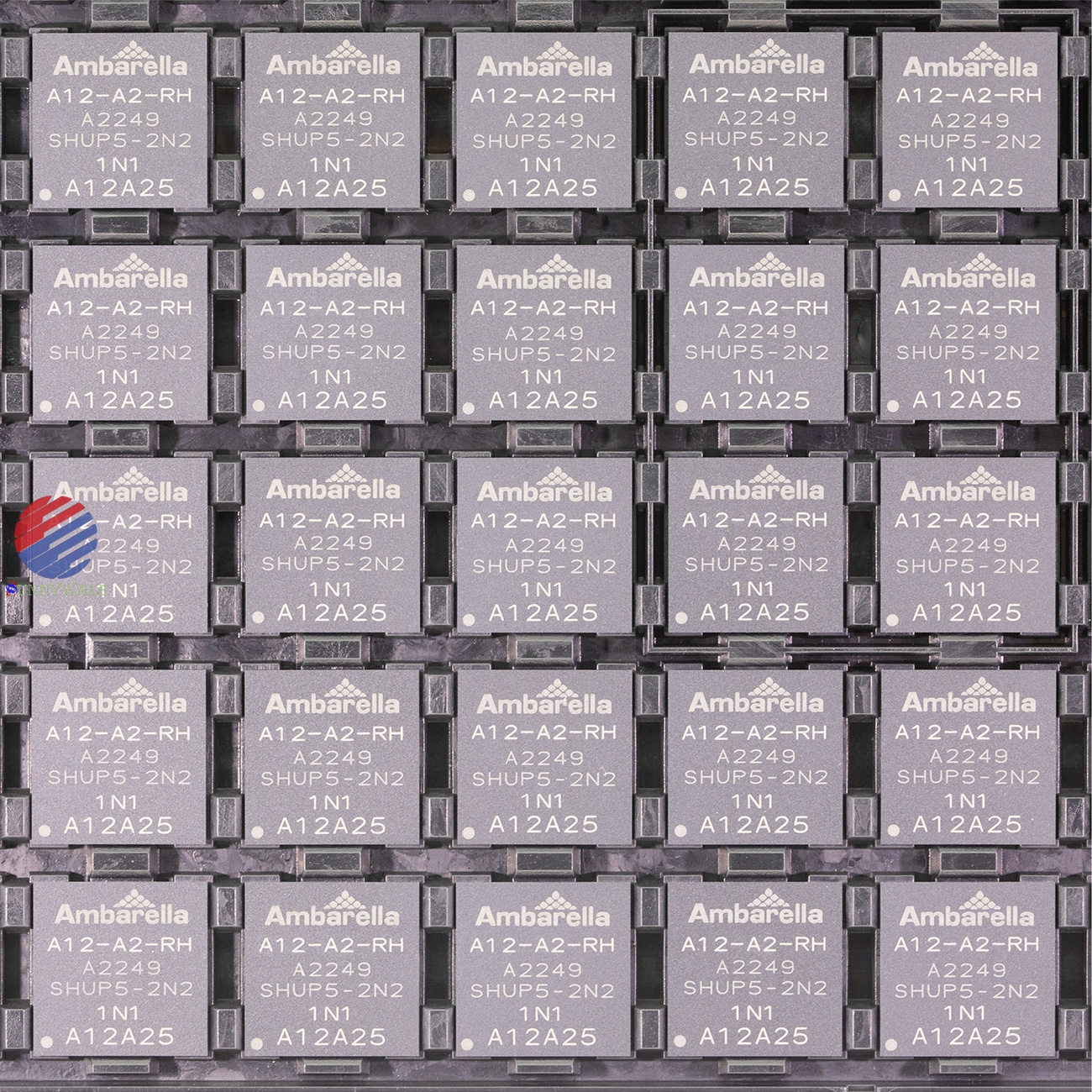

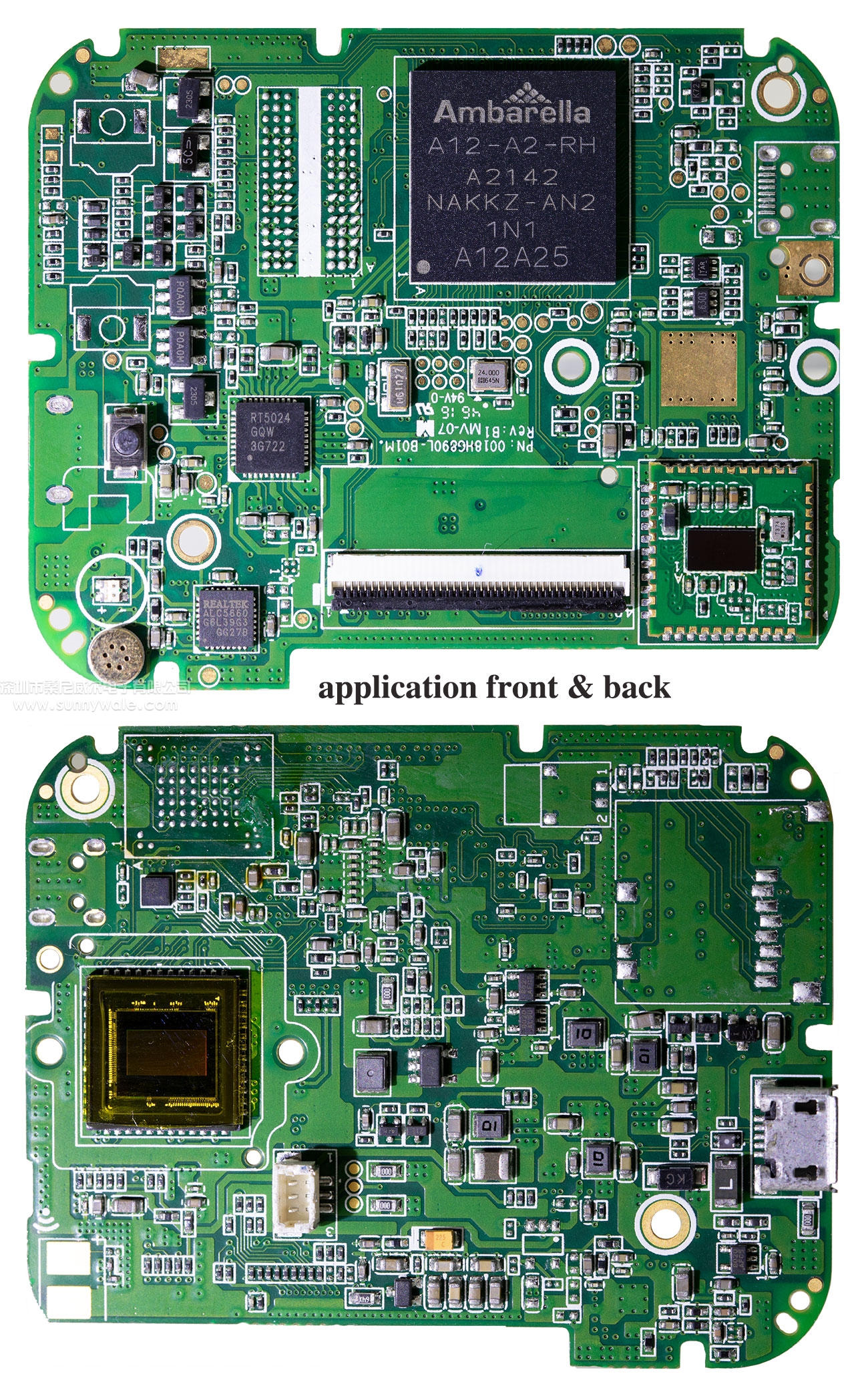

A12A25-A2-RH,Ambarella car video recorder controller, driving accident forensics recording CPU, camera video DSP (digital signal processor), ISP(Image signal processor), H.264 coding engine

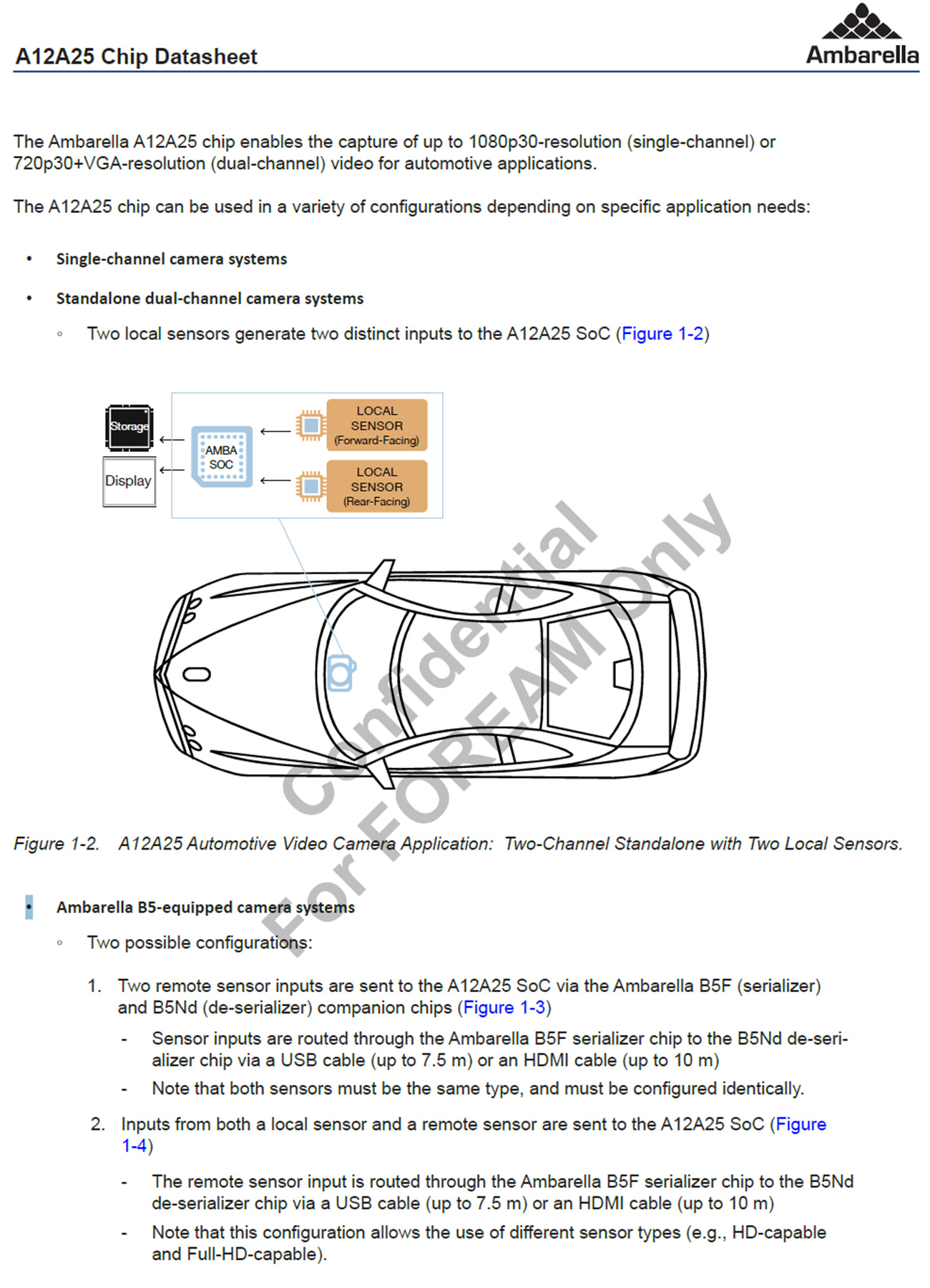

● Ambarella B5-equipped camera systems

○ Two possible configurations:

1. Two remote sensor inputs are sent to the A12A25 Soc via the Ambarella b5F (serializer)

and b5Nd (de-serializer) companion chips (Figure 1-3)

- Sensor inputs are routed through the Ambarella b5F serializer chip to the b5Nd de-seri-

alizer chip via a USb cable (up to 7.5 m) or an HDmI cable (up to 10 m)

- Note that both sensors must be the same type, and must be configured identically.

2. Inputs from both a local sensor and a remote sensor are sent to the A12A25 Soc (Figure

1-4)

- The remote sensor input is routed through the Ambarella b5F serializer chip to the b5Nd

de-serializer chip via a USb cable (up to 7.5 m) or an HDmI cable (up to 10 m)

- Note that this configuration allows the use of different sensor types (e.g., HD-capable

and Full-HD-capable).

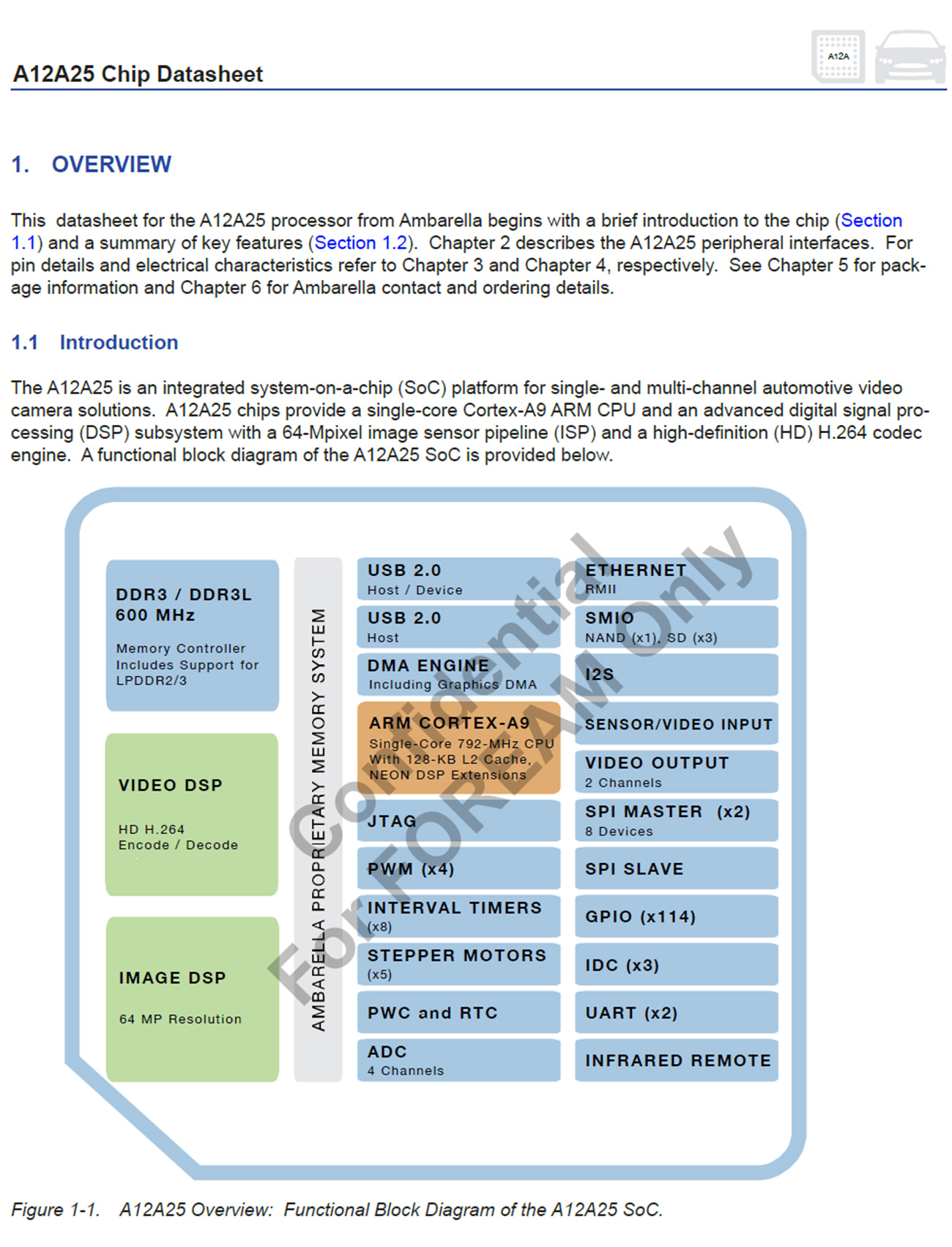

The A12A25 Soc provides a glueless interface to Serial Sub-LVDS, HiSPi, and mIPI interfaces, as well as paral-

lel connections to popular cmOS image sensors. The ISP offers advanced image-processing features, includ-

ing improved multi-exposure high-dynamic-range (HDR) processing, wide dynamic range (WDR) local contrast

enhancement, 3D motion-compensated noise reduction (mcTF), edge enhancement, 3A, and dewarping.

The H.264 codec engine delivers versatile encoding up to 1080p30 total performance in a single-channel con-

figuration. The high-efficiency H.264 encoder implements progressive refresh for low-latency operations, as well

as advanced Main and High-Profile functions for the highest-quality and lowest possible bitrate. These functions

include bidirectional prediction (B-frames), large motion-estimation search range, and macroblock-level quanti-

zation. Ambarella builds in flexibility with a multi-streaming function, allowing on-the-fly start/stop as well as the

adjustment of the bitrate, frame rate, and GOP of each individual stream. The A12A25 WiFi module supports

fast-action capture with loop recording, remote view finders, and remote control by handheld devices.

A 792-MHz ARM Cortex-A9 CPU with NEON DSP extensions and floating point support is available for imple-

menting full-featured user applications.

The A12A25 chip is part of the A12 series of Ambarella Socs. The A12 family is fabricated using low-power 28-

nm cmOS technology and integrates advanced power-saving modes, such as utilizing DSP-subsystem memory

resources to reduce external memory bandwidth and total camera system power requirements.

1.2 Feature List

Features of the A12A25 chip include:

● Embedded single-core ARm cortex-A9 cPU

○ Clock frequency up to 792-MHz

○ 32-Kbyte data / 32-Kbyte instruction cache

○ 128-Kbyte L2 cache

○ NEON SImD engine

● DDR3 and DDR3L controller

○ Up to 600-mHz clock rate

○ Includes support for the LPDDR2 and LPDDR3 low-power DDR interfaces

● Image pipeline

○ more than 480 mPixel/s processing rate

○ 64-mPixel maximum resolution

○ Fish-eye lens dewarping and barrel distortion correction

○ black level correction

○ Dynamic and static defect pixel cluster correction

○ CFA crosstalk and fixed-pattern noise reduction

○ RGb bayer demosaicing

○ Lens shading

○ 3D LUT color transform with gamma

○ Advanced motion-compensated sharpening

○ Advanced dynamic range (WDR and HDR) engine with multi-exposure processing and motion

artifact reduction

○ Per-pixel local exposure dynamic range enhancement

○ Tone mapping and global tone-curve adjustment

○ chromatic aberration correction

○ Flexible APIs and image-tuning tools

○ Adjustable 3A; exposure, white balance and focus control (AE/AWb/AF)

○ Day/Night and Dc/P iris control

○ Crop, mirror, flip, 90o/270o rotation

● Video engine

○ H.264 mP/HP Level 5.1 and mJPEG codecs

○ Maximum encode performance:

- 1080p30 in a single-channel configuration

- 720p30+VGA in a dual-channel configuration (or 1080p30+USb cam)

- 1280x720p60

○ Advanced H.264 compression tools

- I, IP, IbP modes (m=1,2,3,4…; IP, IbP, IbbP, IbbbP…)

- High Profile with B-frames and hierarchical GOP

- Up to three reference frames

○ Flexible rate control

- cbR, VbR and constant QP with max bitrate control

- Macroblock-level adaptive quantization

○ 3D noise reduction (mcTF)

● Sensor/Video Input (VIN) interfaces

○ Two input channels with multiple input modes

- Primary channel supports up to 8-lane SLVS / HiSPi input and up to 4-lane mIPI input

- Secondary channel supports up to 2-lane SLVS / HiSPi / mIPI input

- In SVLS mode the two input channels may be combined to support a single 10-lane SLVS /

HiSPi sensor

- Support for 14-bit parallel and LVcmOS sensors

○ Support for popular CMOS sensors: Sony, ON Semiconductor (Aptina), Panasonic, OmniVision

○ Two clocking options (PLL-generated GcLK_VIN or SLVS bit clock)

○ 16-bit ccIR.601 video input with external sync signals

○ 8-bit, 10-bit, 12-bit or 14-bit bT.656-style video input with embedded sync codes including full-

data-range support

● Video Output (VOUT) interfaces

○ Two logical channels to drive three video output ports

- One logical channel drives HDmI or analog

- One logical channel drives digital

○ Support for RGbA and YUVA OSD

○ Video DAc for 480i/576i composite PAL/NTSc output

○ bT.656-style embedded sync YUV output (8-bit or 16-bit mode)

○ HDmI 1.4b output with consumer Electronics control (cEc) and on-chip PHY

● AHb bus DmA controller

○ memory-to-memory transfers including support for transfers between memory and peripherals

○ Programmable transfer count up to 4 mb

○ DmA scatter/gather via chained descriptor list in memory with DmA control information source

● Dedicated DmA co-processor for graphics and image operations

○ Offers linear copy, 2-D copy, composite, and alpha-blend image operations

○ Supports 4- to 32-bit pixel formats

● I2S digital audio interface (stereo)

○ Audio record/playback

● Ethernet mAc controller

○ IEEE 802.3 compliant with full- and half-duplex (IEEE 802.3x flow-control) and Jumbo frames

○ IEEE 802.1Q VLAN tag detection

○ checksum off-load for received IP and TcP/UDP packets

○ Dedicated pins for RmII or mII interface

○ FIFO (2 Kb / 2 Kb) and DmA support

● Two USb 2.0 interfaces

○ One host port and one additional port configurable as host or device, each with built-in PHY

● Flexible Storage media Input / Output (SmIO) interface

○ NAND Flash controller

- Up to 8-Gbit device, 512-byte and 2-Kbyte page sizes

- 8-bit flash chip data bus

- 4-bit and 8-bit SLC with ECC hardware and read-confirm support

- bcH error correction and increased spare area available

○ Three SD controllers (SD0, SD1, SD2)

- SD0:

● SDIO v3.0, SD, SDHc, SDXc, mmc and emmc operation with boot support and UHS-I speed

- SD1:

● SDIO v3.0, SD, SDHc, SDXc, mmc and emmc operation

- SD2:

● SDIO v1.0, SD, SDHc, SDXc, mmc and emmc operation

- 1-bit, 4-bit and 8-bit SD modes, cRc7 for command and cRc16 for data integrity

● multiple boot options

Proprietary and Confidential 7

A12A25 Chip Datasheet

○ NOR-SPI, NAND Flash, USb and emmc

● Vector interrupt controller including VIC CPU-offload functionality

● SSI / SPI controller interfaces

○ Two SSI / SPI masters with DmA support for up to eight device enables

○ One dedicated SSI / SPI slave port to connect to an external system master

● Two-wire serial Inter-Integrated circuit (I2c / IDc) interfaces (x3)

○ Configurable IDC buses (x2)

○ One IDc bus dedicated for use with HDmI

● UART interfaces (x2)

○ One interface supports flow control

○ One interface supports flow control

● Up to 114 General Purpose Input/Output (GPIO) pins with individual pull-up/down control

● ADc (four channels) with high/low threshold interrupt generation and 12-bit resolution

● Built-in power controller for power-up/down sequencing

● Real Time clock (RTc)

● Interval timing with eight general-purpose timers configurable as external event counters

● Watchdog timer

● Stepper motor interface (five channels) with four-channel Micro-Stepper interface

● Pulse Width modulators (PWm) (x4)

● JTAG In-circuit Emulator (IcE) interface for debugging

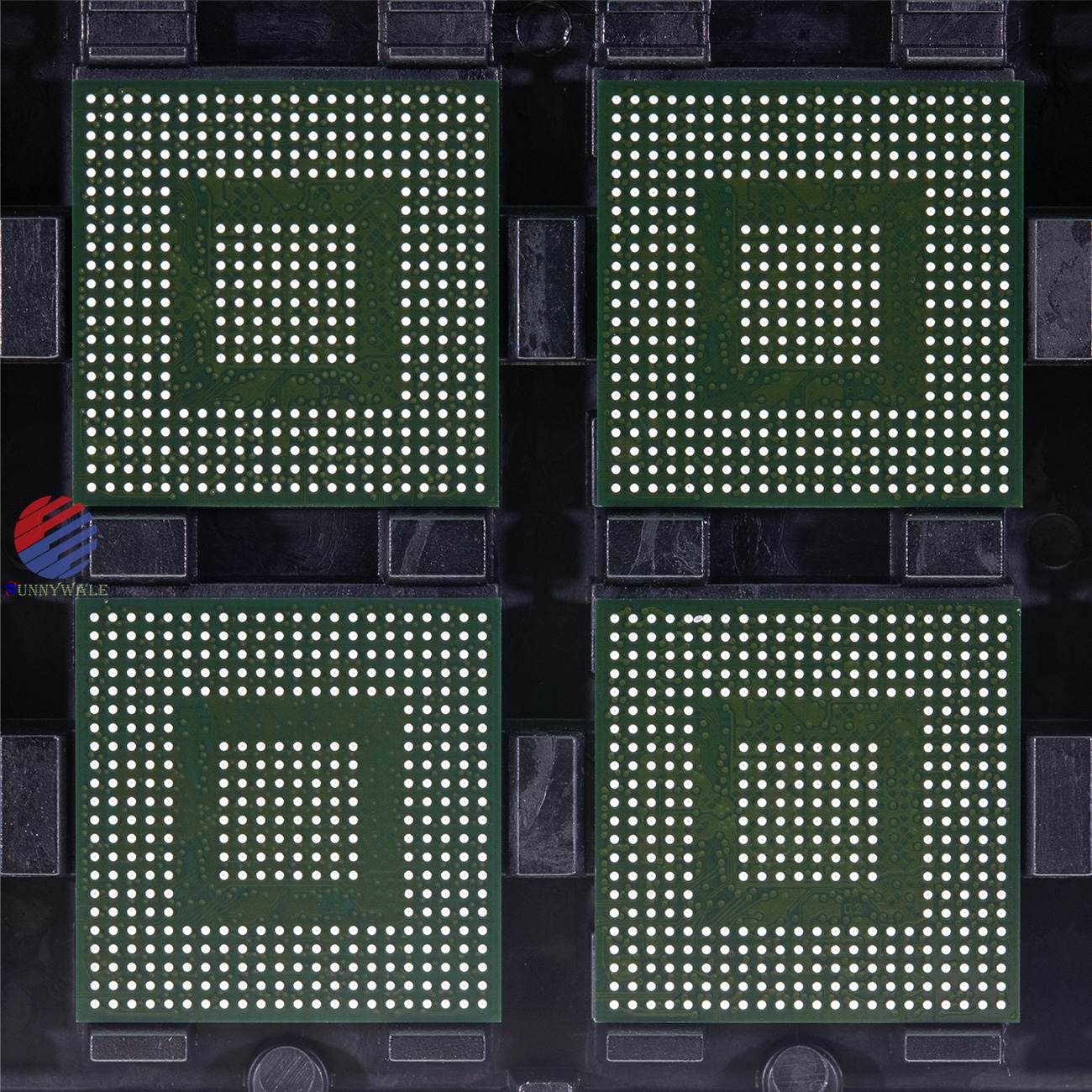

● 404-pin, 0.65-mm pitch LFbGA package (15 mm x 15 mm)

● 28-nm cmOS Low Power (LP) technology

● Operating temperature from -20 c to +85 c

2. INTERFACES

2.1 Overview

This section summarizes the peripheral interfaces for the A12A25 chip as follows:

● (Section 2.2) SDRAm Interface

● (Section 2.3) Video Input (VIN) Interface

● (Section 2.4) Video Output (VOUT) Interfaces

● (Section 2.5) I2S Audio Interface

● (Section 2.6) Ethernet Interface

● (Section 2.7) USb Interfaces

● (Section 2.8) Smart media Input/Output (SmIO) Interface

● (Section 2.9) SSI / SPI Interface

● (Section 2.10) IDc / I2c Interface

● (Section 2.11) UART Interface

● (Section 2.12) General Purpose Input/Output (GPIO) Interface

● (Section 2.13) Analog-to-Digital converter (ADc) Interface

● (Section 2.14) Power controller (PWc) and Real Time clock (RTc) Interfaces

● (Section 2.15) Stepper, micro-Stepper, and Pulse Width modulator (PWm) Interfaces

● (Section 2.16) JTAG Interface

2.2 SDRAM Interface

The A12A25 chip includes a synchronous DRAm interface, enabling high data-access rates in response to pipe-

lined commands. The features of the A12A25 SDRAM interface include:

● Frequencies up to 600 MHz

● Support for DDR3 and DDR3L operations

● Support for the LPDDR2/3 low-power DDR interface

● Programmable I/O strength

Please contact an Ambarella representative to select a qualified Ambarella-approved DDR component.

2.3 Video Input (VIN) Interface

The A12A25 chip supports two input channels, each with multiple serial and parallel input modes. The features of

the A12A25 VIN interface include:

● Support for up to 8-lane SLVS / HiSPi input and up to 4-lane mIPI cSI input in the primary channel

● Up to 2-lane SLVS / HiSPi / mIPI inputs in the secondary channel

- Note that the secondary VIN interface may not be supported in software. Please con-

tact Ambarella for more information about the use of the secondary VIN channel.

● Support for a single 10-lane SLVS / HiSPi sensor when the two input channels are combined

● Support for 14-bit parallel and LVcmOS sensors

● 16-bit ccIR.601 video input with external sync signals

● 8-bit, 10-bit, 12-bit or 14-bit bT.656-style video input with embedded sync codes including full-data-

range support