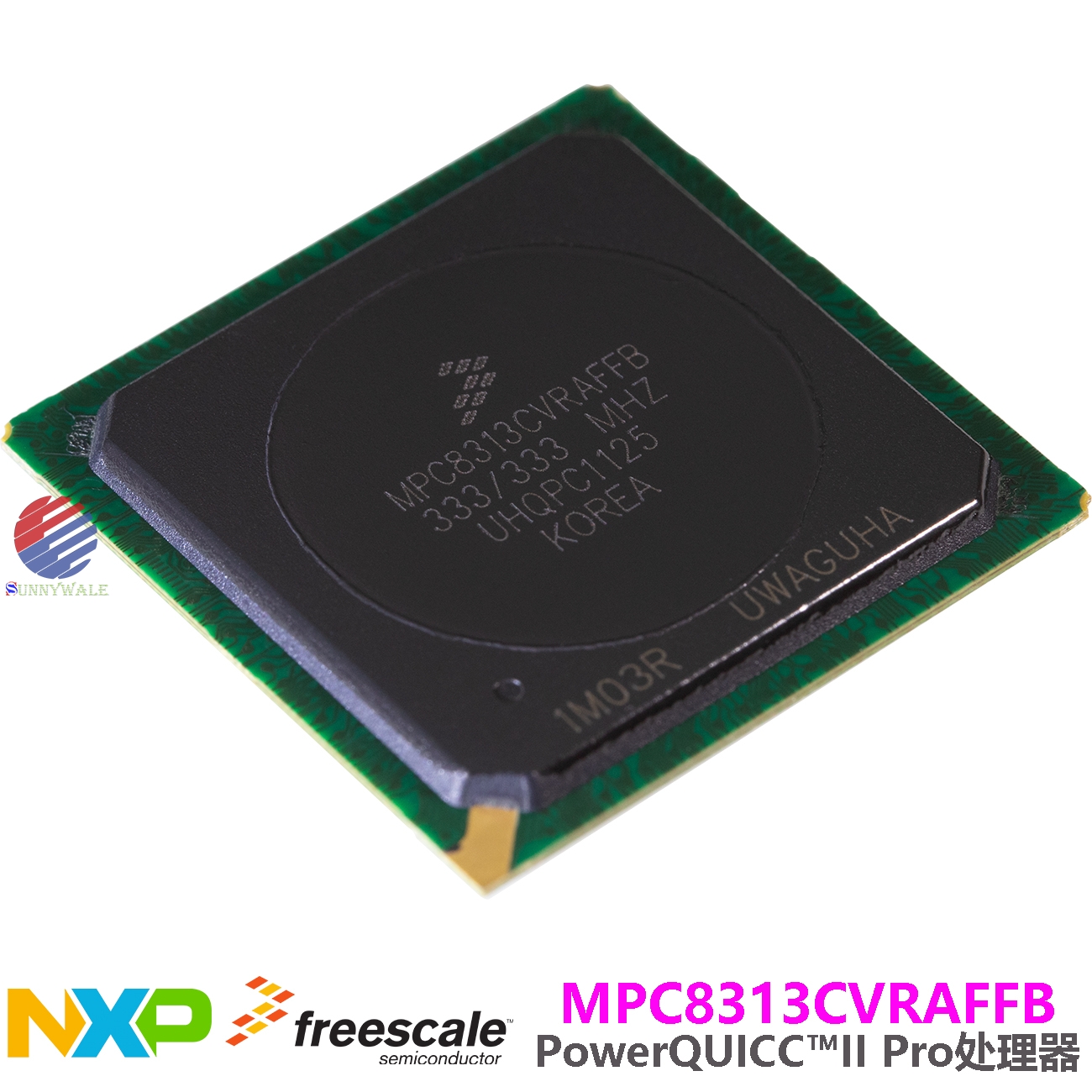

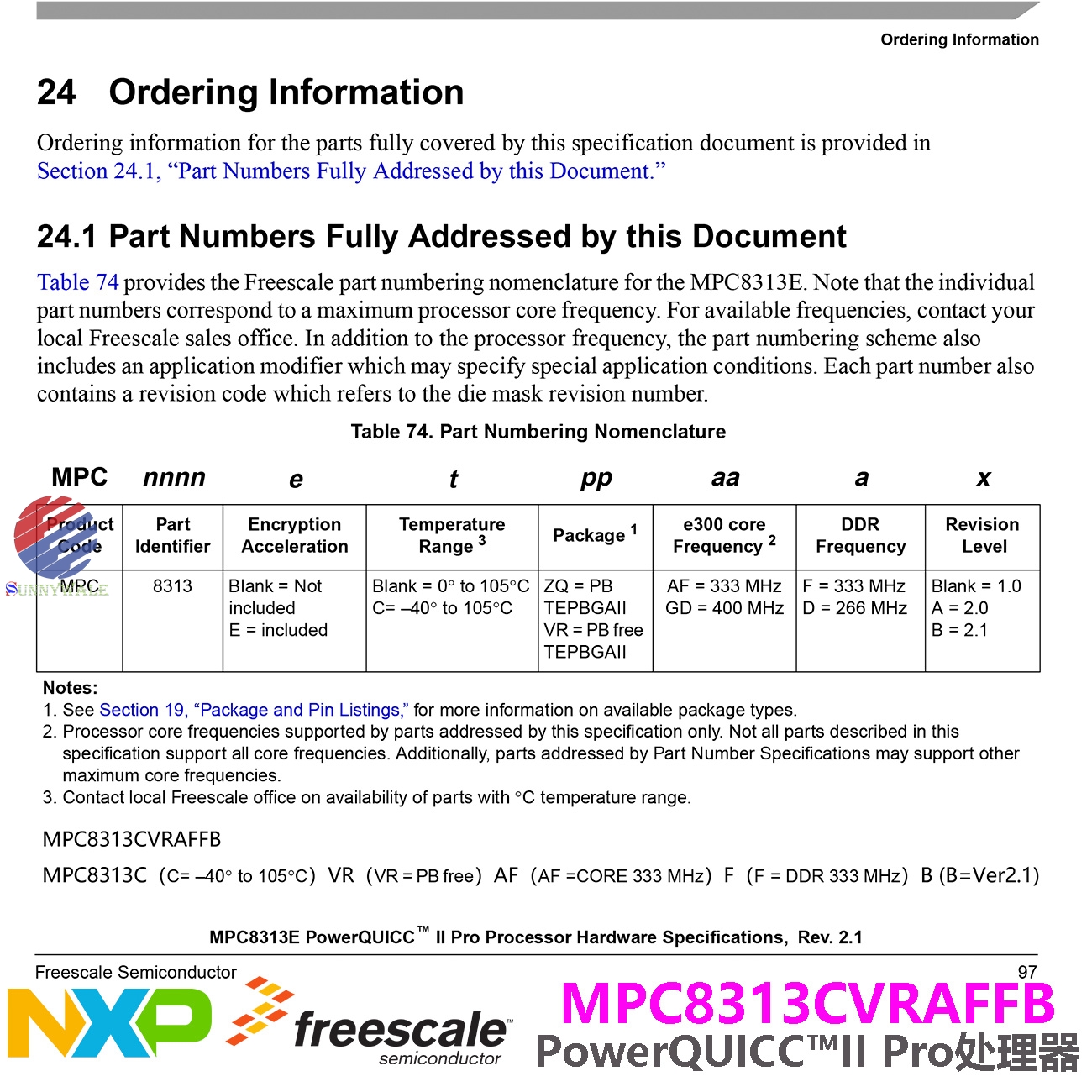

MPC8313CVRAFFB NXP Freescale Semiconductor PowerQUICC™ II Pro Processor

This document provides an overview of the MPC8313CVRAFFB PowerQUICC™ II Pro processor features, including a block diagram showing the major functional components. The MPC8313CVRAFFB is a cost-effective, low-power, highly integrated host processor that addresses the requirements of several printing and imaging, consumer, and industrial applications, including main CPUs and I/O processors in printing systems, networking switches and line cards, wireless LANs (WLANs), network access servers (NAS), VPN routers, intelligent NIC, and industrial controllers. The MPC8313E extends the PowerQUICC™ family, adding higher CPU performance, additional functionality, and faster interfaces while addressing the requirements related to time-to-market, price, power consumption, and package size.

The MPC8313CVRAFFB security engine (SEC 2.2) allows CPU-intensive cryptographic operations to be offloaded from the main CPU core. The security-processing accelerator provides hardware acceleration for the DES, 3DES, AES, SHA-1, and MD-5 algorithms.

1.01 MPC8313CVRAFFB Features

The following features are supported in the MPC8313E:

• Embedded PowerPC™ e300 processor core built on Power Architecture™ technology; operates at up to 333 MHz.

• High-performance, low-power, and cost-effective host processor

• DDR1/DDR2 memory controller—one 16-/32-bit interface at up to 333 MHz supporting both DDR1 and DDR2

• 16-Kbyte instruction cache and 16-Kbyte data cache, a floating point unit, and two integer units

• Peripheral interfaces such as 32-bit PCI interface with up to 66-MHz operation, 16-bit enhanced local bus interface with up to 66-MHz operation, and USB 2.0 (full speed) with an on-chip PHY.

• Security engine provides acceleration for control and data plane security protocols

• Power management controller for low-power consumption

• High degree of software compatibility with previous-generation PowerQUICC processor-based designs for backward compatibility and easier software migration

1.02 MPC8313CVRAFFB Serial Interfaces

The following interfaces are supported in the MPC8313E: dual UART, dual I2C, and an SPI interface

1.03 Security Engine

The security engine is optimized to handle all the algorithms associated with IPSec, IEEE Std 802.11i®, and iSCSI. The security engine contains one crypto-channel, a controller, and a set of crypto execution units (EUs). The execution units are as follows:

• Data encryption standard execution unit (DEU), supporting DES and 3DES

• Advanced encryption standard unit (AESU), supporting AES

• Message digest execution unit (MDEU), supporting MD5, SHA1, SHA-224, SHA-256, and HMAC with any algorithm

• One crypto-channel supporting multi-command descriptor chains

1.04 DDR Memory Controller

The MPC8313E DDR1/DDR2 memory controller includes the following features:

• Single 16- or 32-bit interface supporting both DDR1 and DDR2 SDRAM

• Support for up to 333 MHz

• Support for two physical banks (chip selects), each bank independently addressable

• 64-Mbit to 1-Gbit devices with x8/x16/x32 data ports (no direct x4 support)

• Support for one 16-bit device or two 8-bit devices on a 16-bit bus, or one 32-bit device or two 16-bit devices on a 32-bit bus

• Support for up to 16 simultaneous open pages

• Supports auto refresh

• On-the-fly power management using CKE

• 1.8-/2.5-V SSTL2 compatible I/O

1.05 PCI Controller

The MPC8313CVRAFFB PCI controller includes the following features:

• PCI specification revision 2.3 compatible

• Single 32-bit data PCI interface operates at up to 66 MHz

• PCI 3.3-V compatible (not 5-V compatible)

• Support for host and agent modes

• On-chip arbitration, supporting three external masters on PCI

• Selectable hardware-enforced coherenc

1.06 USB Dual-Role Controller

The MPC8313CVRAFFB USB controller includes the following features:

• Supports USB on-the-go mode, which includes both device and host functionality, when using an external ULPI (UTMI + low-pin interface) PHY

• Compatible with Universal Serial Bus Specification, Rev. 2.0

• Supports operation as a stand-alone USB device

- Supports one upstream facing port

- Supports three programmable USB endpoints

• Supports operation as a stand-alone USB host controller

- Supports USB root hub with one downstream-facing port

- Enhanced host controller interface (EHCI) compatible

• Supports full-speed (12 Mbps), and low-speed (1.5 Mbps) operation. Low-speed operation is

supported only in host mode.

• Supports UTMI + low pin interface (ULPI) or on-chip USB 2.0 full-speed PHY

1.07 Dual Enhanced Three-Speed Ethernet Controllers (eTSECs)

The MPC8313CVRAFFB eTSECs include the following features:

• Two RGMII/SGMII/MII/RMII/RTBI interfaces

• Two controllers designed to comply with IEEE Std 802.3®, 802.3u®, 802.3x®, 802.3z®, 802.3au®, and 802.3ab®

• Support for Wake-on-Magic Packet™, a method to bring the device from standby to full operating mode

• MII management interface for external PHY control and status

• Three-speed support (10/100/1000 Mbps)

• On-chip high-speed serial interface to external SGMII PHY interface

• Support for IEEE Std 1588™

• Support for two full-duplex FIFO interface modes

• Multiple PHY interface configuration

• TCP/IP acceleration and QoS features available

• IP v4 and IP v6 header recognition on receive

• IP v4 header checksum verification and generation

• TCP and UDP checksum verification and generation

• Per-packet configurable acceleration

• Recognition of VLAN, stacked (queue in queue) VLAN, IEEE Std 802.2®, PPPoE session, MPLS stacks, and ESP/AH IP-security headers

• Transmission from up to eight physical queues.

• Reception to up to eight physical queue

• Full- and half-duplex Ethernet support (1000 Mbps supports only full-duplex):

- IEEE 802.3 full-duplex flow control (automatic PAUSE frame generation or

software-programmed PAUSE frame generation and recognition)

- Programmable maximum frame length supports jumbo frames (up to 9.6 Kbytes) and

IEEE 802.1 virtual local area network (VLAN) tags and priority

- VLAN insertion and deletion

- Per-frame VLAN control word or default VLAN for each eTSEC

- Extracted VLAN control word passed to software separately

- Retransmission following a collision

- CRC generation and verification of inbound/outbound packets

- Programmable Ethernet preamble insertion and extraction of up to 7 bytes

• MAC address recognition:

- Exact match on primary and virtual 48-bit unicast addresses

- VRRP and HSRP support for seamless router fail-over

- Up to 16 exact-match MAC addresses supported

- Broadcast address (accept/reject)

- Hash table match on up to 512 multicast addresses

- Promiscuous mode

• Buffer descriptors backward compatible with MPC8260 and MPC860T 10/100 Ethernet programming models

• RMON statistics support

• 10-Kbyte internal transmit and 2-Kbyte receive FIFOs

• MII management interface for control and statu

1.08 Programmable Interrupt Controller (PIC)

The programmable interrupt controller (PIC) implements the necessary functions to provide a flexible solution for general-purpose interrupt control. The PIC programming model supports 5 external and 34 internal discrete interrupt sources. Interrupts can also be redirected to an external interrupt controller.

1.09 Power Management Controller (PMC)

The MPC8313E power management controller includes the following features:

• Provides power management when the device is used in both host and agent modes

• Supports PCI power management 1.2 D0, D1, D2, D3hot, and D3cold states

• On-chip split power supply controlled through external power switch for minimum standby power

• Support for PME generation in PCI agent mode, PME detection in PCI host mode

• Supports wake-up from Ethernet (Magic Packet), USB, GPIO, and PCI (PME input as host)

1.10 Serial Peripheral Interface (SPI)

The serial peripheral interface (SPI) allows the MPC8313E to exchange data between other PowerQUICC family chips, Ethernet PHYs for configuration, and peripheral devices such as EEPROMs, real-time clocks, A/D converters, and ISDN devices.

The SPI is a full-duplex, synchronous, character-oriented channel that supports a four-wire interface (receive, transmit, clock, and slave select). The SPI block consists of transmitter and receiver sections, an

independent baud-rate generator, and a control unit.

1.11 DMA Controller, Dual I2C, DUART, Local Bus Controller, and Timers

The MPC8313CVRAFFB provides an integrated four-channel DMA controller with the following features:

• Allows chaining (both extended and direct) through local memory-mapped chain descriptors (accessible by local masters)

• Supports misaligned transfers

There are two I2C controllers. These synchronous, multi-master buses can be connected to additional devices for expansion and system development.

The DUART supports full-duplex operation and is compatible with the PC16450 and PC16550 programming models. The 16-byte FIFOs are supported for both the transmitter and the receiver.

The MPC8313E local bus controller (LBC) port allows connections with a wide variety of external DSPs and ASICs. Three separate state machines share the same external pins and can be programmed separately to access different types of devices. The general-purpose chip select machine (GPCM) controls accesses to asynchronous devices using a simple handshake protocol. The three user programmable machines (UPMs) can be programmed to interface to synchronous devices or custom ASIC interfaces. Each chip select can be configured so that the associated chip interface can be controlled by the GPCM or UPM controller. The FCM provides a glueless interface to parallel-bus NAND Flash E2PROM devices. The FCM contains three basic configuration register groups-BRn, ORn, and FMR. Both may exist in the same system. The local bus can operate at up to 66 MHz.

The MPC8313CVRAFFB system timers include the following features: periodic interrupt timer, real time clock, software watchdog timer, and two general-purpose timer blocks.

2 Electrical Characteristics

This section provides the AC and DC electrical specifications and thermal characteristics for the MPC8313CVRAFFB. The MPC8313CVRAFFB is currently targeted to these specifications. Some of these specifications are independent of the I/O cell, but are included for a more complete reference. These are not purely I/O buffer design specifications.

2.01 Overall DC Electrical Characteristics

This section covers the ratings, conditions, and other characteristics

MPC8313CVRAFFB Specifications

Product Attribute Attribute Value

Manufacturer: NXP/FREESCALE

Product Category: Microprocessors - MPU

RoHS: Details

Core: e300c3

Number of Cores: 1 Core

Data Bus Width: 32 bit

Maximum Clock Frequency: 333 MHz

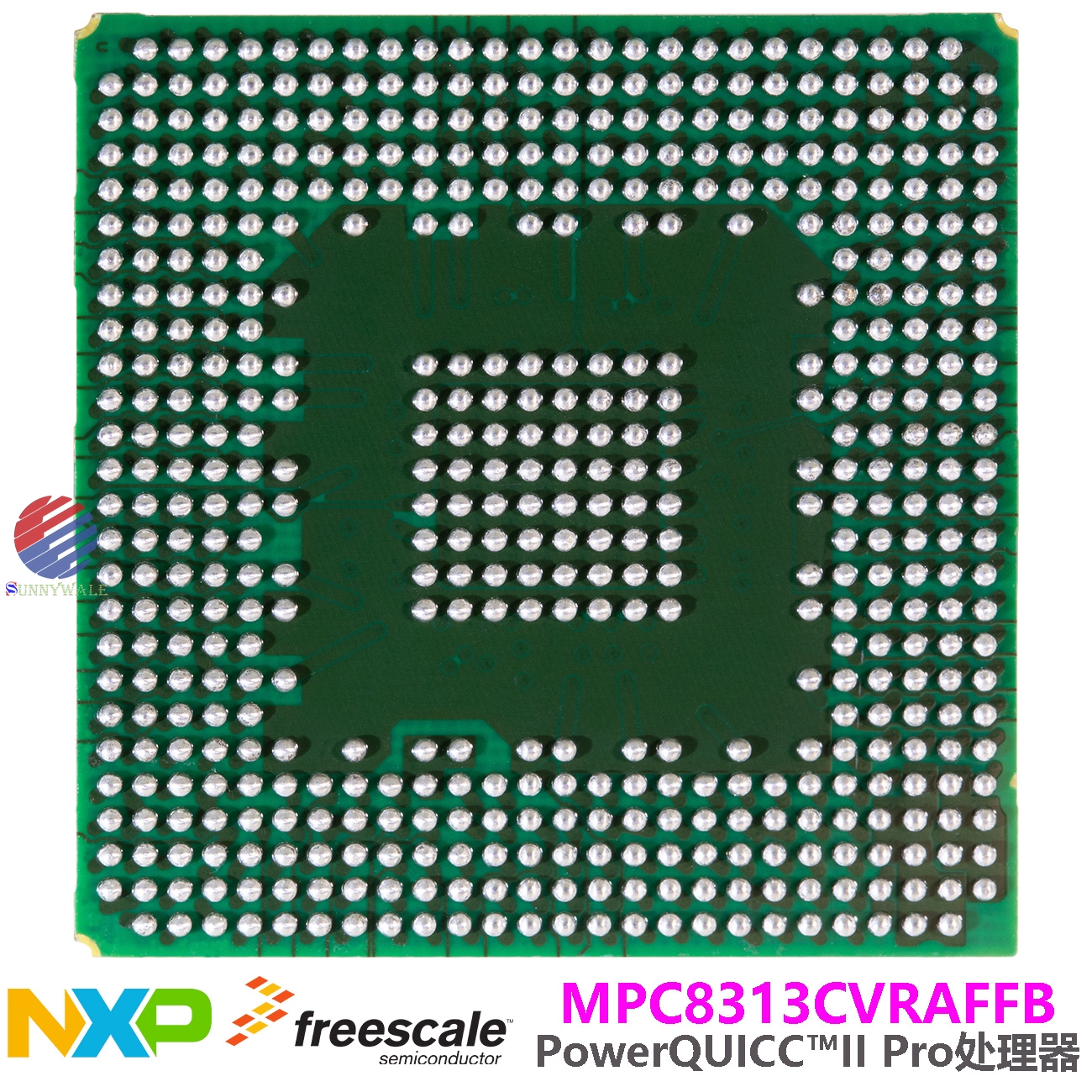

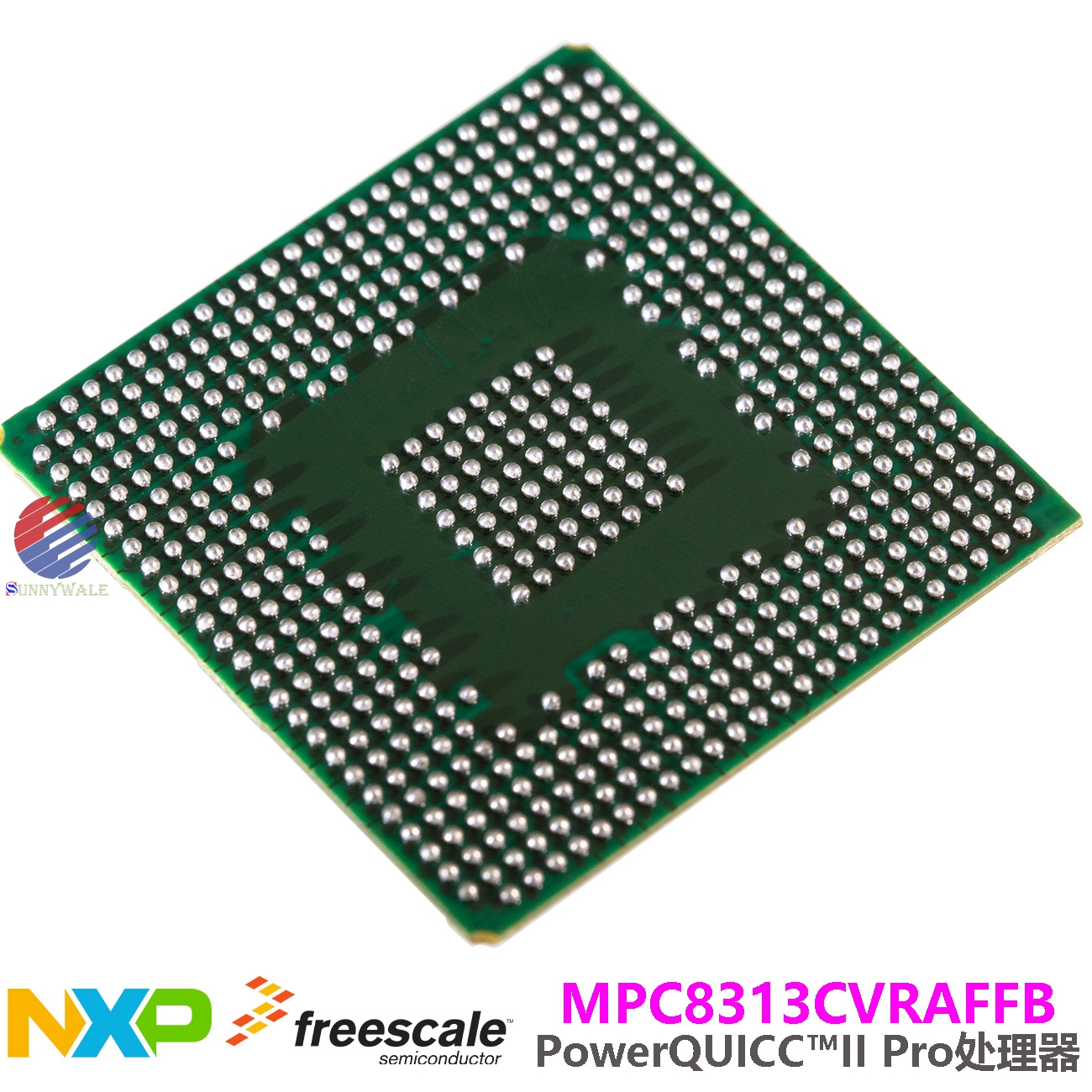

Package/Case: PBGA-516

L1 Cache Instruction Memory: 16 kB

L1 Cache Data Memory: 16 kB

Operating Supply Voltage: 1 V

Mounting Style: SMD/SMT

Minimum Operating Temperature: - 40 C

Maximum Operating Temperature: + 105 C

Qualification: AEC-Q100

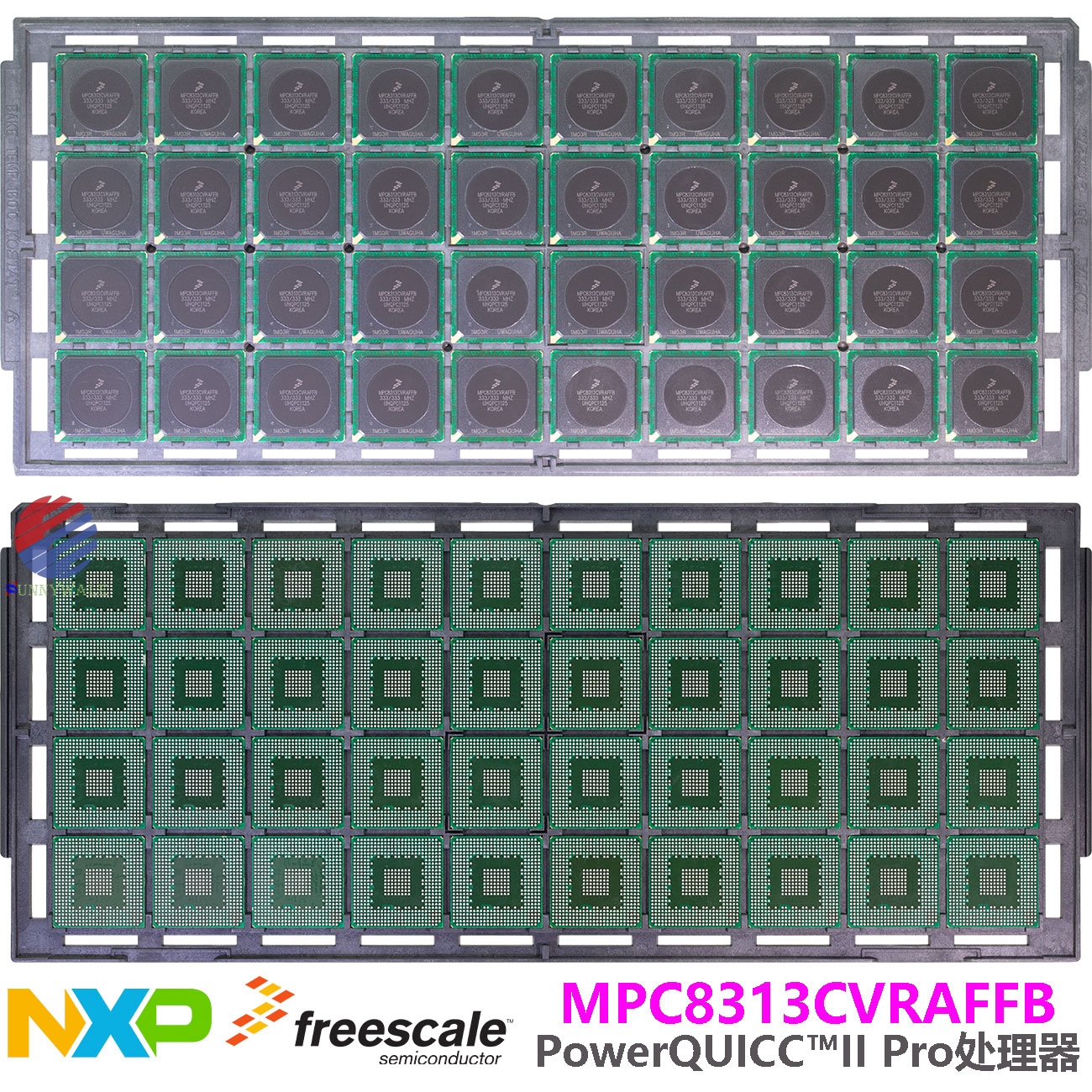

Packaging: Tray

Brand: NXP Semiconductors

I/O Voltage: 1.8 V, 2.5 V, 3.3 V

Instruction Type: Floating Point

Interface Type: Ethernet, I2C, PCIe, SPI, UART, USB

Memory Type: L1 Cache

Moisture Sensitive: Yes

Number of Timers/Counters: 2 Timer

Processor Series: PowerQUICC II Pro

Product Type: Microprocessors - MPU

Factory Pack Quantity:40

Subcategory: Microprocessors - MPU

Watchdog Timers: Watchdog Timer

Unit Weight:

5.497 g

All of the above pictures are taken after matting the online showing, what you see is what you get.

Click or copy the link to browser free download the MPC8313CVRAFFB datasheet PDF file.

Freight is free when you buy 2 pieces in China, if you have MPC8313CVRAFFB inventory, you can sell to me, if you need buy MPC8313CVRAFFB, you can ask me to buy.

If you want to know about similar products MPC8313E, or click here,or Visit The official website:

sunnywale.com,Search the keywods“8313E”,it can show more details.

For more details and HD images, please copy the following link to open in your browser to view our official website;or visit our official website:

Sunnywale.com , searching keyword "MPC8313".

If you want to read the introduction in English, please Clict the

中文版

Buy now MPC8313CVRAFFB