# 1/3-Inch CMOS Digital Image Sensor

#### **AR0330 Data Sheet**

For the latest data sheet, from Sunnywale's Web site: www.sunnywale.com

#### **Features**

- 2.2µm pixel with Aptina™ A-Pix technology

- Full HD support at 60 fps (2304H x 1296V) for maximum video performance

- Superior low-light performance

- 3.4M (3:2) and 3.15M (4:3)still images

- Support for external mechanical shutter

- · Support for external LED or Xenon flash

- Data interfaces: four-lane serial high-speed pixel interface (HiSPi<sup>TM</sup>) differential signaling (SLVS), four-lane serial MIPI interface, or parallel.

- Slow-motion video (WVGA 240 fps)

- On-chip phase-locked loop (PLL) oscillator

- Integrated position-based color and lens shading correction

- Simple two-wire serial interface

- Auto black level calibration

- 12-to-10 bit output A-Law compression

- · Slave mode for precise frame-rate control

### **Applications**

- 1080p high-definition digital video camcorder

- Web cameras and video conferencing cameras

- Security

### **General Description**

Aptina's AR0330 is a 1/3-inch CMOS digital image sensor with an active-pixel array of 2304Hx1536V. It can support 3.15 megapixel (2048H x 1536V) digital still image capture and a 1080p60+20%EIS (2304H x 1296V) digital video mode. It incorporates sophisticated onchip camera functions such as windowing, mirroring, column and row subsampling modes, and snapshot modes.

Table 1: Key Parameters

| Parameter      | Typical Value                                                                                        |

|----------------|------------------------------------------------------------------------------------------------------|

| Optical format | 1/3-inch (5.8 mm) Note: Sensor optical format will also work with lenses designed for 1/3.2" format. |

Table 1: Key Parameters (continued)

| Parameter            |                                | Typical Value                                                                                                                              |  |  |  |

|----------------------|--------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                      |                                | 2304(H) x 1536(V): (entire array):<br>5.07mm(H) x 3.38mm(V)<br>2048(H) x 1536(V) (4:3, still mode)<br>2304(H) x 1296(V) (16:9, still mode) |  |  |  |

| Pixel size           |                                | 2.2um x 2.2um                                                                                                                              |  |  |  |

| Color filte          | r array                        | RGB Bayer                                                                                                                                  |  |  |  |

| Shutter ty           | rpe                            | ERS and GRR                                                                                                                                |  |  |  |

| Input cloc           | k range                        | 6 – 64 MHz                                                                                                                                 |  |  |  |

| Output cl            | ock maximum                    | 196 Mp/s (4-lane HiSPi or MIPI)<br>98 Mp/s (Parallel)                                                                                      |  |  |  |

| Output<br>Video      | 4-lane HiSPi<br>(196 Mp/s)     | 2304x1296 at 60 fps<br>< 450 mW (HiSPi, Vcм 0.2V)<br>2048x1536 at 54 fps<br>< 450 mW (HiSPi, Vcм 0.2V)                                     |  |  |  |

|                      | 4-lane HiSPi<br>(98 Mp/s)      | 2304x1296 at 30 fps<br>< 300 mW (HiSPi, Vcm 0.2V)<br>2048x1536 at 25 fps<br>< 300 mW (HiSPi, Vcm 0.2V)                                     |  |  |  |

| Responsiv            | vity                           | 1.9 V/lux-sec                                                                                                                              |  |  |  |

| SNR <sub>MAX</sub>   |                                | 39 dB                                                                                                                                      |  |  |  |

| Dynamic              | range                          | 72.4 dB                                                                                                                                    |  |  |  |

| Supply               | I/O                            | 1.8 or 2.8V                                                                                                                                |  |  |  |

| voltage              | Digital                        | 1.8 V                                                                                                                                      |  |  |  |

|                      | Analog                         | 2.8 V                                                                                                                                      |  |  |  |

|                      | HiSPi                          | 0.4V - 0.8V, 1.7V - 1.9V                                                                                                                   |  |  |  |

| Operating (junction) | temperature<br>-T <sub>J</sub> | -30°C to + 70° C                                                                                                                           |  |  |  |

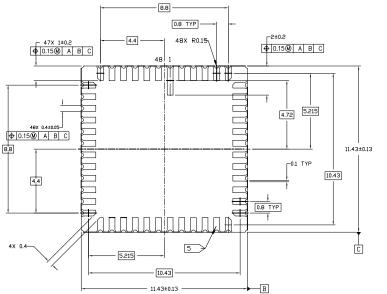

| Package o            | ptions                         | 11.4 mm x 11.4mm CLCC                                                                                                                      |  |  |  |

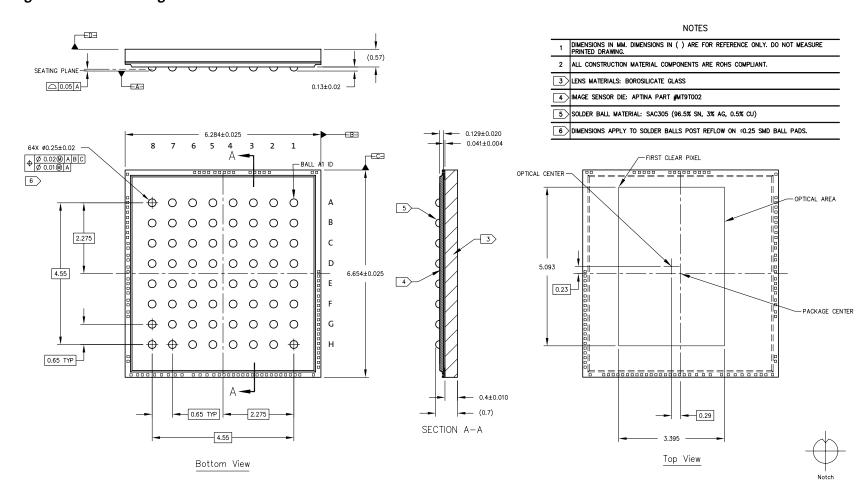

|                      |                                | 6.28 mm x 6.65 mm CSP                                                                                                                      |  |  |  |

|                      |                                | Bare die                                                                                                                                   |  |  |  |

#### **Ordering Information**

Table 2: Available Part Numbers

| Part Number         | Description                    |

|---------------------|--------------------------------|

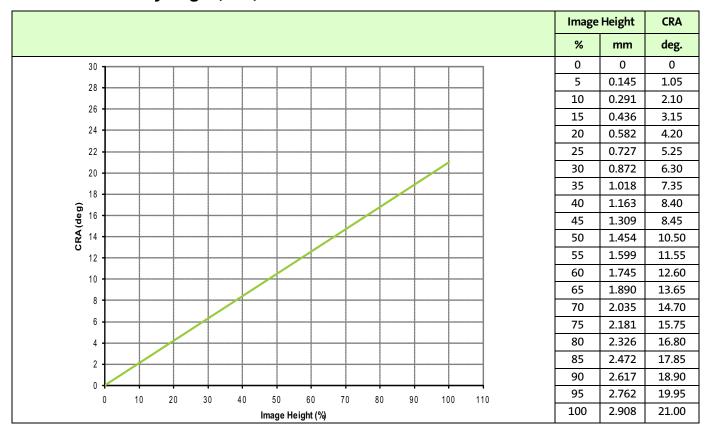

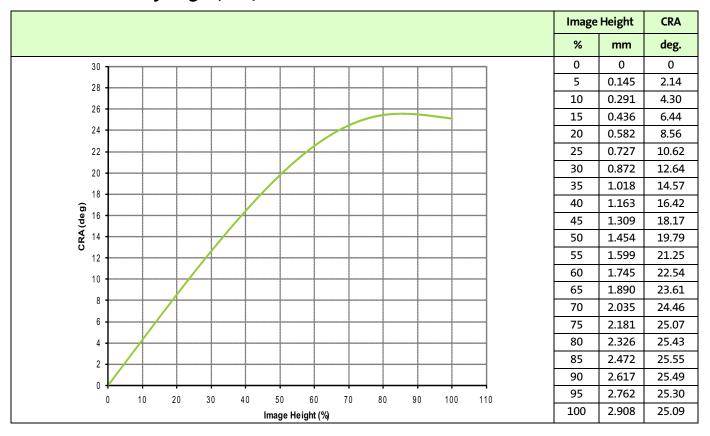

| AR0330CM1C00SHAA0-E | 48pin CLCC (HiSPi/MIPI) 0° CRA |

| AR0330CM1C00SHKA0-E | CSP (HiSPi/MIPI) 0° CRA        |

| AR0330CM1C21SHKA0-E | CSP (HiSPi/MIPI) 21° CRA       |

| AR0330CM1C25SHKA0-E | CSP (HiSPi/MIPI) 25° CRA       |

PDF: 2455415125/Source: 4164066292

AR0330\_DS - Rev. F Pub. 1/11 EN

AR0310\_DS - Rev. F Pub. 1/11 EN

AR0330\_DS - Rev. F Pub. 1/11 EN

AR0310\_DS - Rev. F Pub. 1/11 EN

AR0310\_DS - Rev. F Pub. 1/11 EN

### AR0330: 1/3-Inch CMOS Digital Image Sensor Table of Contents

### **Table of Contents**

| Features                                  |  |

|-------------------------------------------|--|

| Applications                              |  |

| General Description                       |  |

| Ordering Information                      |  |

| General Description                       |  |

| Functional Overview                       |  |

| Working Modes                             |  |

| Pin Descriptions                          |  |

| Sensor Initialization                     |  |

| Power-Up Sequence                         |  |

| Power-Down Sequence                       |  |

| Electrical Characteristics                |  |

| Sequencer                                 |  |

| Sensor PLL                                |  |

| VCO                                       |  |

| Dual Readout Paths                        |  |

| Parallel PLL Configuration                |  |

| Serial PLL Configuration                  |  |

| Pixel Output Interfaces                   |  |

| Parallel Interface                        |  |

| Output Enable Control                     |  |

| Configuration of the Pixel Data Interface |  |

| High Speed Serial Pixel Data Interface    |  |

| HiSPi Physical Layer                      |  |

| DLL Timing Adjustment                     |  |

| HiSPi Streaming Mode Protocol Layer       |  |

| MIPI Interface                            |  |

| Serial ConfigurationPixel Sensitivity     |  |

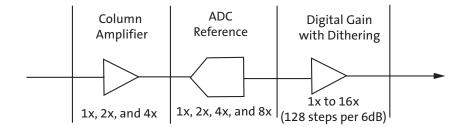

| Gain StagesGain Stages                    |  |

| Data Pedestal                             |  |

| Sensor Readout                            |  |

| Image Acquisition Modes                   |  |

| Window Control                            |  |

| Readout Modes                             |  |

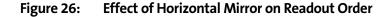

| Horizontal Mirror                         |  |

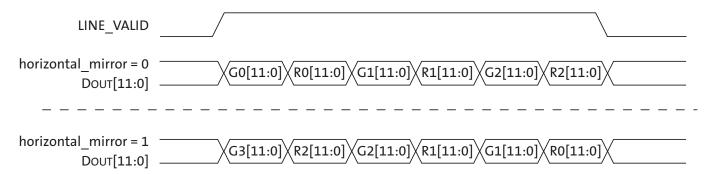

| Vertical Flip                             |  |

| Subsampling                               |  |

| Sensor Frame Rate                         |  |

| Row Period (T <sub>ROW</sub> )            |  |

| Row Periods Per Frame                     |  |

| Slave Mode                                |  |

| Frame Readout                             |  |

| Changing Sensor Modes                     |  |

| Register Changes                          |  |

| Real-Time Context Switching               |  |

| Compression                               |  |

| Test Patterns                             |  |

| Solid Color.                              |  |

| Vertical Color Bars                       |  |

| Walking 1s                                |  |

|                                           |  |

### AR0330: 1/3-Inch CMOS Digital Image Sensor Table of Contents

| Two-Wire Serial Register Interface           | 51 |

|----------------------------------------------|----|

| Protocol                                     |    |

| Start Condition.                             |    |

| Stop Condition                               |    |

| Data Transfer                                |    |

| Slave Address/Data Direction Byte            |    |

| Message Byte                                 |    |

| Acknowledge Bit                              |    |

| No-Acknowledge Bit                           |    |

| Typical Sequence                             |    |

| V1 1                                         |    |

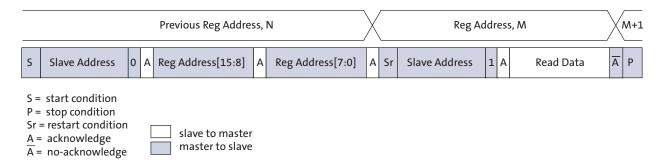

| Single READ From Random Location             |    |

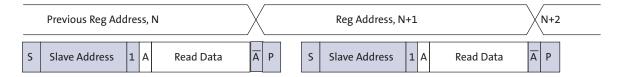

| Single READ From Current Location            |    |

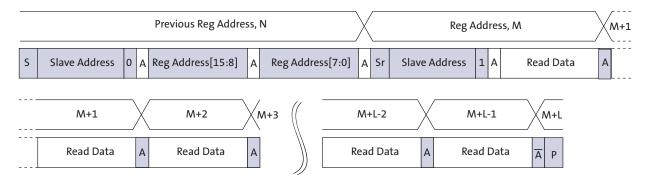

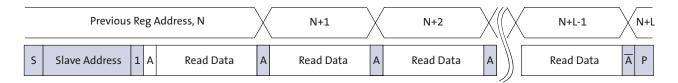

| Sequential READ, Start From Random Location  |    |

| Sequential READ, Start From Current Location | 54 |

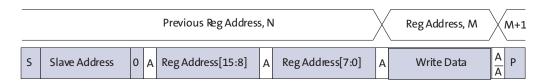

| Single WRITE to Random Location              | 54 |

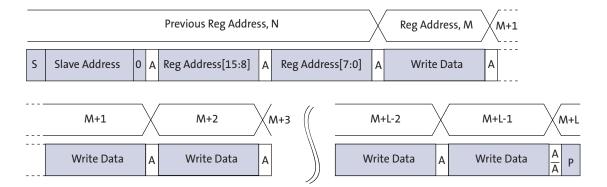

| Sequential WRITE, Start at Random Location   | 55 |

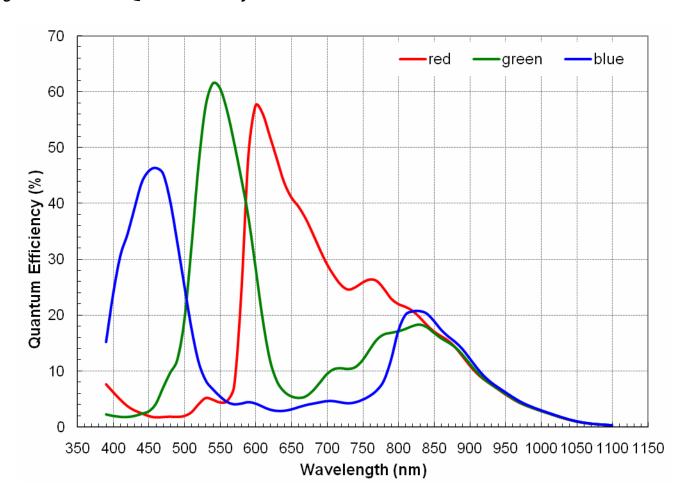

| Spectral Characteristics                     | 56 |

| Read the Sensor CRA                          |    |

| Packages                                     |    |

| CLCC Package                                 |    |

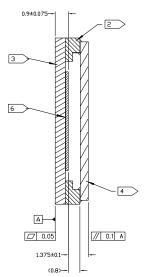

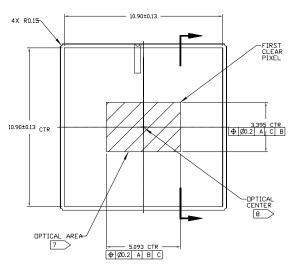

| CSP Package.                                 |    |

| Revision History.                            |    |

### AR0330: 1/3-Inch CMOS Digital Image Sensor List of Figures

### **List of Figures**

| Figure 1:  | Block Diagram                                                                       | 6  |

|------------|-------------------------------------------------------------------------------------|----|

| Figure 2:  | Typical Configuration: Serial Four-Lane HiSPi Interface                             |    |

| Figure 3:  | Typical MIPI Connections                                                            |    |

| Figure 4:  | Typical Configuration: Parallel Pixel Data Interface                                |    |

| Figure 5:  | CLCC Package Pin Descriptions                                                       | 13 |

| Figure 6:  | Power Up                                                                            |    |

| Figure 7:  | Power Down                                                                          | 16 |

| Figure 8:  | Two-WIre Serial Bus Timing Parameters                                               | 18 |

| Figure 9:  | I/O Timing Diagram                                                                  | 19 |

| Figure 10: | HiSPi Eye Diagram for Both Clock and Data Signals                                   | 21 |

| Figure 11: | HiSPi Skew Between Data Signals Within the PHY                                      | 22 |

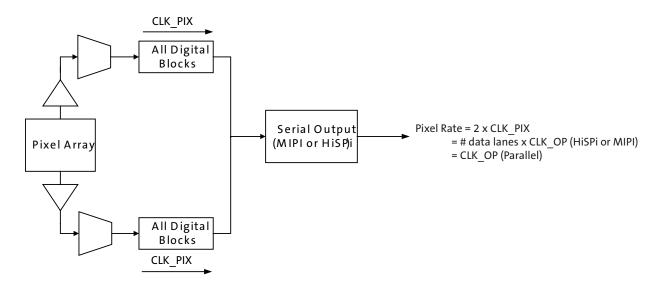

| Figure 12: | Relationship Between Readout Clock and Peak Pixel Rate                              | 23 |

| Figure 13: | Sensor Dual Readout Paths                                                           |    |

| Figure 14: | PLL for the Parallel Interface                                                      | 24 |

| Figure 15: | PLL for the Serial Interface                                                        | 25 |

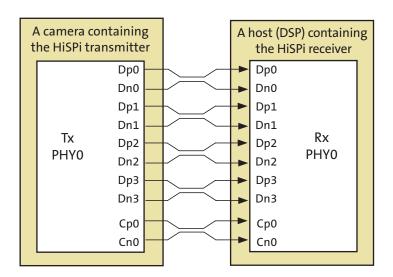

| Figure 16: | HiSPi Transmitter and Receiver Interface Block Diagram                              |    |

| Figure 17: | Timing Diagram                                                                      | 29 |

| Figure 18: | Block Diagram of DLL Timing Adjustment                                              | 29 |

| Figure 19: | Delaying the clock_lane with Respect to data_lane                                   | 30 |

| Figure 20: | Delaying data_lane with Respect to the clock_lane                                   | 30 |

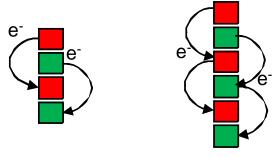

| Figure 21: | Integration Control in ERS Readout                                                  | 32 |

| Figure 22: | Example of 8.33ms Integration in 16.6ms Frame                                       |    |

| Figure 23: | Row Read and Row Reset Showing Fine Integration                                     | 33 |

| Figure 24: | The Row Integration Time is Greater Than the Frame Readout Time                     | 34 |

| Figure 25: | Gain Stages in AR0330 Sensor                                                        |    |

| Figure 26: | Effect of Horizontal Mirror on Readout Order                                        |    |

| Figure 27: | Effect of Vertical Flip on Readout Order                                            | 37 |

| Figure 28: | Horizontal Binning in the AR0330 Sensor                                             | 38 |

| Figure 29: | Vertical Row Binning in the AR0330 Sensor                                           | 38 |

| Figure 30: | Frame Period Measured in Clocks                                                     |    |

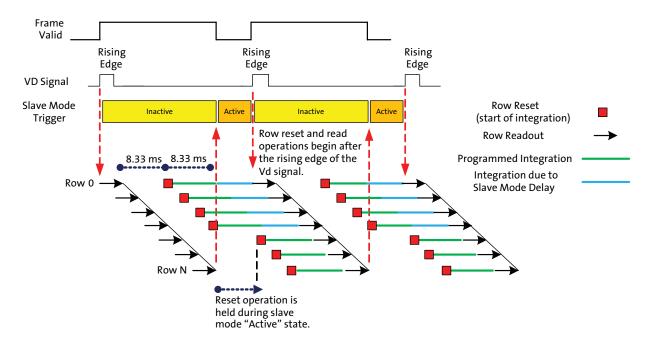

| Figure 31: | Slave Mode Active State and Vertical Blanking                                       |    |

| Figure 32: | Slave Mode Example with Equal Integration and Frame Readout Periods                 | 44 |

| Figure 33: | Slave Mode Example Where the Integration Period is Half of the Frame Readout Period | 45 |

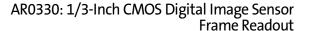

| Figure 34: | Example of the Sensor Output of a 2304 x 1296 Frame at 60 fps                       | 46 |

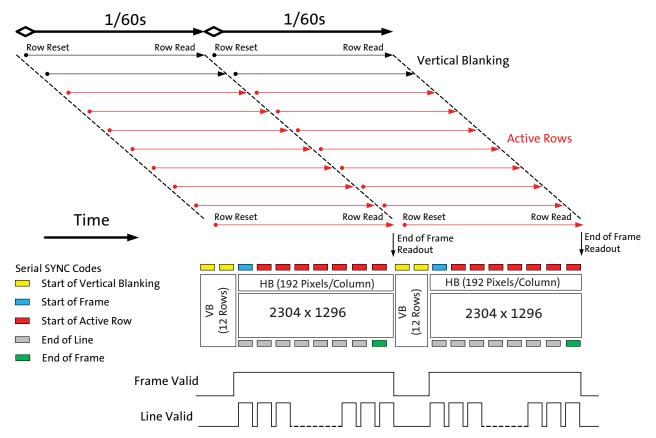

| Figure 35: | Example of the Sensor Output of a 2304 x1296 Frame at 30 fps                        | 47 |

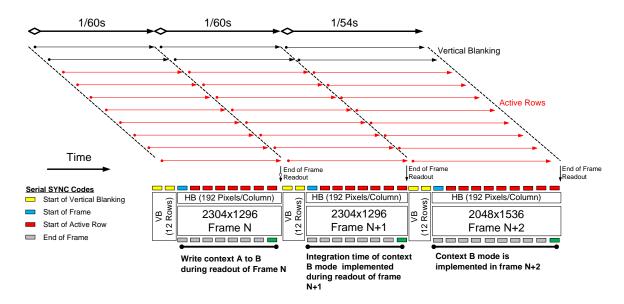

| Figure 36: | Example of Changing the Sensor from Context A to Context B                          | 48 |

| Figure 37: | Single READ From Random Location                                                    | 53 |

| Figure 38: | Single READ From Current Location                                                   |    |

| Figure 39: | Sequential READ, Start From Random Location                                         |    |

| Figure 40: | Sequential READ, Start From Current Location.                                       |    |

| Figure 41: | Single WRITE to Random Location.                                                    | 54 |

| Figure 42: | Sequential WRITE, Start at Random Location                                          | 55 |

| Figure 43: | Bare Die Quantum Efficiency.                                                        |    |

| Figure 44: | CLCC Package                                                                        |    |

| Figure 45: | CSP Package                                                                         | 60 |

## AR0330: 1/3-Inch CMOS Digital Image Sensor List of Tables

### **List of Tables**

| Table 1:  | Key Parameters                                                                | 1  |

|-----------|-------------------------------------------------------------------------------|----|

| Table 2:  | Available Part Numbers                                                        | 1  |

| Table 3:  | Available Aspect Ratios in the AR0330 Sensor                                  | 7  |

| Table 4:  | Available Working Modes in the AR0330 Sensor                                  | 7  |

| Table 5:  | Pin Descriptions                                                              | 11 |

| Table 6:  | CSP Package Pin Descriptions                                                  | 12 |

| Table 7:  | Power-Up Sequence                                                             | 15 |

| Table 8:  | Power-Down Sequence                                                           | 16 |

| Table 9:  | DC Electrical Definitions and Characteristics                                 | 17 |

| Table 10: | Absolute Maximum Ratings                                                      | 17 |

| Table 11: | Two-Wire Serial Register Interface Electrical Characteristics                 | 18 |

| Table 12: | Two-Wire Serial Register Interface Timing Specification                       | 18 |

| Table 13: | I/O Parameters                                                                | 19 |

| Table 14: | I/O Timing                                                                    | 20 |

| Table 15: | Parallel I/O Rise Slew Rate                                                   |    |

| Table 16: | HiSPi Rise and Fall Times at 660 Mbps                                         |    |

| Table 17: | HiSPi Rise and Fall Times at 360 MHz                                          |    |

| Table 18: | Channel, PHY and Intra-PHY Skew                                               |    |

| Table 19: | Clock DLL Steps                                                               |    |

| Table 20: | Data DLL Steps                                                                |    |

| Table 21: | PLL Parameters for the Parallel Interface                                     |    |

| Table 22: | Example PLL Configuration for the Parallel Interface                          |    |

| Table 23: | PLL Parameters for the Serial Interface                                       |    |

| Table 24: | Example PLL Configurations for the Serial Interface                           |    |

| Table 25: | Output Enable Control                                                         |    |

| Table 26: | Configuration of the Pixel Data Interface                                     |    |

| Table 27: | Recommended MIPI Timing Configuration                                         |    |

| Table 28: | Recommended Sensor Gain Tables                                                |    |

| Table 29: | Recommended Registers to Configure Sensor Gain Table                          |    |

| Table 30: | Available Skip and Bin Modes in the AR0330 Sensor                             |    |

| Table 31: | Configuration for Horizontal Subsampling                                      |    |

| Table 32: | Configuration for Vertical Subsampling                                        |    |

| Table 33: | Minimum Vertical Blanking Configuration                                       |    |

| Table 34: | Serial SYNC Codes Included with Each Protocol Included with the AR0330 Sensor |    |

| Table 35: | List of Configurable Registers for Context A and Context B                    |    |

| Table 36: | A-Law Compression Table for 12-10 bits.                                       |    |

| Table 37: | Test Pattern Modes                                                            |    |

| Table 38: | Chief Ray Angle (CRA) 21 °                                                    |    |

| Table 39: | Chief Ray Angle (CRA) 25 °                                                    | 58 |

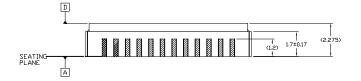

| Table 40: | CRA Value                                                                     | 58 |

AR0330: 1/3-Inch CMOS Digital Image Sensor General Description

### **General Description**

The Aptina® AR0330 can be operated in its default mode or programmed for frame size, exposure, gain, and other parameters. The default mode output is a 2304 x 1296 image at 60 frames per second (fps). The sensor outputs 10- or 12-bit raw data, using either the parallel or serial (HiSPi, MIPI) output ports.

#### **Functional Overview**

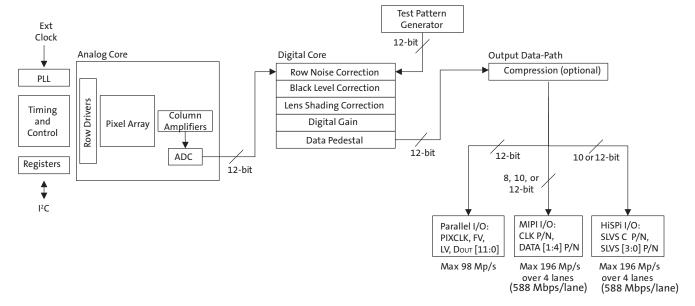

The AR0330 is a progressive-scan sensor that generates a stream of pixel data at a constant frame rate. It uses an on-chip, phase-locked loop (PLL) that can generate all internal clocks from a single master input clock running between 6 and 64 MHz. The maximum output pixel rate is 196 Mp/s using a 4-lane HiSPi or MIPI serial interface and 98 Mp/s using the parallel interface. Figure 1 shows a block diagram of the sensor.

Figure 1: Block Diagram

User interaction with the sensor is through the two-wire serial bus, which communicates with the array control, analog signal chain, and digital signal chain. The core of the sensor is a 3.4Mp active- pixel sensor array. The timing and control circuitry sequences through the rows of the array, resetting and then reading each row in turn. In the time interval between resetting a row and reading that row, the pixels in the row integrate incident light. The exposure is controlled by varying the time interval between reset and readout. Once a row has been read, the signal from the column is amplified in a column amplifier and then digitized in an analog-to-digital converter(ADC). The output from the ADC is a 12-bit value for each pixel in the array. The ADC output passes through a digital processing signal chain (which provides further data path corrections and applies digital gain).

AR0330: 1/3-Inch CMOS Digital Image Sensor Working Modes

# **Working Modes**

The AR0330 sensor working modes are specified from the following aspect ratios:

Table 3: Available Aspect Ratios in the AR0330 Sensor

|       | Aspect Ratio    | Sensor Array Usage  |

|-------|-----------------|---------------------|

| 4:3   | Still Format #1 | 2256 (H) x 1296 (V) |

| 16:10 | Still Format #2 | 2256 (H) x 1504 (V) |

| 16:9  | HD Format       | 2304 (H) x 1296 (V) |

The AR0330 supports the following working modes. To operate the sensor at full speed (196 Mp/s) the sensor must use the 4-lane HiSPi or MIPI interface. The sensor will operate at half-speed (98 Mp/s) when using the parallel interface.

Table 4: Available Working Modes in the AR0330 Sensor

| Mode                      | Aspect Ratio | Active Readout<br>Window | Sensor Output<br>Resolution | FPS<br>(4-Lane MIPI/HiSPi<br>Interface) | FPS<br>(Parallel<br>Interface) | Sub-<br>sampling | FOV  |

|---------------------------|--------------|--------------------------|-----------------------------|-----------------------------------------|--------------------------------|------------------|------|

| 1080p + EIS               | 16:9         | 2304 x 1296              | 2304 x 1296                 | 60                                      | n/a                            | -                | 100% |

|                           |              |                          |                             | 30                                      | 30                             | -                | 100% |

| 3M Still                  | 4:3          | 2048 x 1536              | 2048 x 1536                 | 30                                      | 30                             | -                | 100% |

|                           | 3:2          | 2256 x 1504              | 2256 x 1504                 | 30                                      | 25                             | -                | 100% |

| WVGA + EIS                | 16:9         | 2304 x 1296              | 1152 x 648                  | 60                                      | 60                             | 2x2              | 100% |

| WVGA + EIS<br>Slow-motion | 16:9         | 2304 x 1296              | 1152 x 648                  | 120                                     | 120                            | 2x2              | 100% |

| VGA Video                 | 16:10        | 2256 x 1440              | 752 x 480                   | 60                                      | 60                             | 3x3              | 96%  |

| VGA Video<br>Slow-mo      | 16:10        | 2256 x 1440              | 752 x 480                   | 240                                     | 240                            | 3x3              | 96%  |

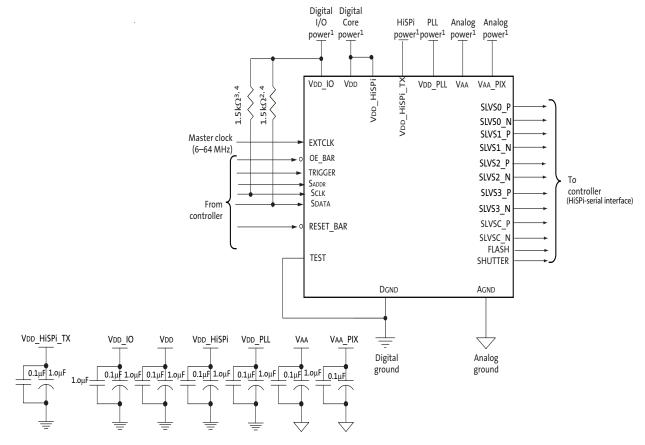

Figure 2: Typical Configuration: Serial Four-Lane HiSPi Interface

- 1. All power supplies must be adequately decoupled. Aptina recommends having 1.0μF and 0.1μF decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: VAA, VAA\_PIX, VDD\_PLL,VDD\_IO, and VDD. Actual values and results may vary depending on layout and design considerations.

- 2. To allow for space constraints, Aptina recommends having  $0.1\mu\text{F}$  decoupling capacitor inside the module as close to the pads as possible. In addition, place a  $10\mu\text{F}$  capacitor for each supply off-module but close to each supply.

- 3. Aptina recommends a resistor value of  $1.5k\Omega$ , but a greater value may be used for slower two-wire speed.

- 4. The pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 5. Aptina recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. TEST pin should be tied to DGND.

- 7. Set High\_VCM (R0x306E[9]) to 0 (default) to use the VDD\_HiSPi\_TX in the range of 0.4 0.8V. Set High\_VCM to 1 to use a range of 1.7 1.9V.

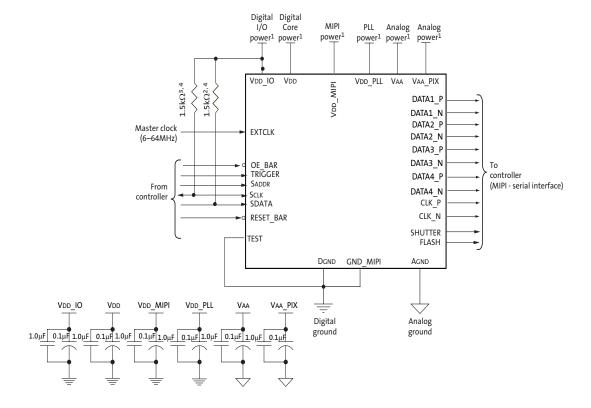

Figure 3: Typical MIPI Connections

- 1. All power supplies must be adequately decoupled. Aptina recommends having 1.0µF and 0.1µF decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: VAA, VAA\_PIX, VDD\_PLL, VDD\_MIPI, VDD\_IO, and VDD. Actual values and results may vary depending on layout and design considerations.

- 2. To allow for space constraints, Aptina recommends having  $0.1\mu\text{F}$  decoupling capacitor inside the module as close to the pads as possible. In addition, place a  $10\mu\text{F}$  capacitor for each supply off-module but close to each supply.

- 3. Aptina recommends a resistor value of 1.5k $\Omega$ , but a greater value may be used for slower two-wire speed.

- 4. The pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 5. Aptina recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. TEST pin must be tied to DGND for the MIPI configuration.

- 7. Aptina recommends that GND MIPI be tied to DGND.

- 8. VDD\_MIPI can be connected to VDD\_IO if VDD\_IO=2.8V. Otherwise, VDD\_MIPI can be tied to VDD\_PLL if the Aptina-recommended decoupling capacitors are used. VDD\_MIPI is tied to VDD\_PLL in both the CLCC and the CSP package. Aptina strongly recommends that VDD\_MIPI must be connected to a 2.8V supply and kept separate from VAA and VAA PIX.

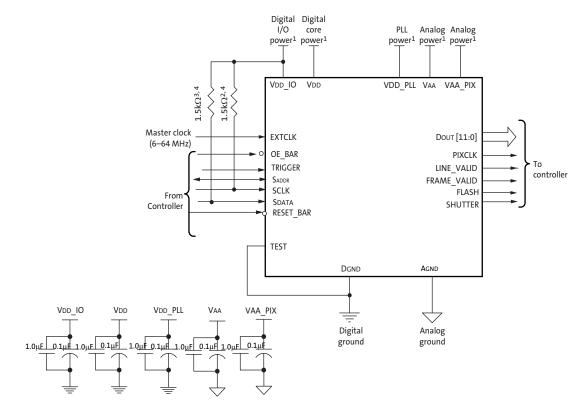

Figure 4: Typical Configuration: Parallel Pixel Data Interface

- 1. All power supplies must be adequately decoupled. Aptina recommends having  $1.0\mu F$  and  $0.1\mu F$  decoupling capacitors for every power supply. If space is a concern, then priority must be given in the following order: VAA, VAA\_PIX, VDD\_PLL, VDD\_IO, and VDD. Actual values and results may vary depending on layout and design considerations.

- 2. To allow for space constraints, Aptina recommends having  $0.1\mu F$  decoupling capacitor inside the module as close to the pads as possible. In addition, place a  $10\mu F$  capacitor for each supply off-module but close to each supply.

- 3. Aptina recommends a resistor value of 1.5k $\Omega$ , but a greater value may be used for slower two-wire speed.

- 4. The pull-up resistor is not required if the controller drives a valid logic level on SCLK at all times.

- 5. Aptina recommends that analog power planes are placed in a manner such that coupling with the digital power planes is minimized.

- 6. TEST pin should be tied to DGND.

AR0330: 1/3-Inch CMOS Digital Image Sensor Pin Descriptions

# **Pin Descriptions**

### Table 5: Pin Descriptions

| Name         | Туре   | Description                                                                                                                               |  |  |

|--------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| RESET_BAR    | Input  | Asynchronous reset (active LOW). All settings are restored to factory default.                                                            |  |  |

| EXTCLK       | Input  | Master input clock, range 6 -64 MHz                                                                                                       |  |  |

| OE BAR       | Input  | Output enable(active LOW).                                                                                                                |  |  |

| TRIGGER      | Input  | Receives slave mode VD signal for frame rate synchronization and trigger to start a GRR frame.                                            |  |  |

| SADDR        | Input  | Two-wire serial address select.                                                                                                           |  |  |

| Sclk         | Input  | Two-wire serial clock input.                                                                                                              |  |  |

| Sdata        | I/O    | Two-wire serial data I/O.                                                                                                                 |  |  |

| PIXCLK       | Output | Pixel clock out. Dout is valid on rising edge of this clock.                                                                              |  |  |

| Douт[11:0]   | Output | Parallel pixel data output.                                                                                                               |  |  |

| FLASH        | Output | Flash output. Synchronization pulse for external light source. Can be left floating if not used.                                          |  |  |

| FRAME_VALID  | Output | Asserted when DOUT data is valid.                                                                                                         |  |  |

| LINE VALID   | Output | Asserted when Dout data is valid.                                                                                                         |  |  |

| VDD          | Power  | Digital power.                                                                                                                            |  |  |

| VDD_IO       | Power  | IO supply power.                                                                                                                          |  |  |

| VDD_PLL      | Power  | PLL power supply. The MIPI power supply (VDD MIPI) is tied to VDD PLL in both packages.                                                   |  |  |

| DGND         | Power  | Digital GND.                                                                                                                              |  |  |

| VAA          | Power  | Analog power.                                                                                                                             |  |  |

| VAA_PIX      | Power  | Pixel power.                                                                                                                              |  |  |

| AGND         | Power  | Analog GND.                                                                                                                               |  |  |

| TEST         | Input  | Enable manufacturing test modes. Tie to DGND for normal sensor operation.                                                                 |  |  |

| SHUTTER      | Output | Control for external mechanical shutter. Can be left floating if not used.                                                                |  |  |

| SLVS0_P      | Output | HiSPi serial data, lane 0, differential P.                                                                                                |  |  |

| SLVS0_N      | Output | HiSPi serial data, lane 0, differential N.                                                                                                |  |  |

| SLVS1 P      | Output | liSPi serial data, lane 1, differential P.                                                                                                |  |  |

| SLVS1_N      | Output | HiSPi serial data, lane 1, differential N.                                                                                                |  |  |

| SLVS2_P      | Output | HiSPi serial data, lane 2, differential P.                                                                                                |  |  |

| SLVS2_N      | Output | HiSPi serial data, lane 2, differential N.                                                                                                |  |  |

| SLVS3_P      | Output | HiSPi serial data, lane 3, differential P.                                                                                                |  |  |

| SLVS3_N      | Output | HiSPi serial data, lane 3, differential N.                                                                                                |  |  |

| SLVSC P      | Output | HiSPi serial DDR clock differential P.                                                                                                    |  |  |

| SLVSC_N      | Output | HiSPi serial DDR clock differential N.                                                                                                    |  |  |

| DATA1_P      | Output | MIPI serial data, lane 1, differential P                                                                                                  |  |  |

| DATA1_N      | Output | MIPI serial data, lane 1, differential N                                                                                                  |  |  |

| DATA2_P      | Output | MIPI serial data, lane 2, differential P                                                                                                  |  |  |

| DATA2_N      | Output | MIPI serial data, lane 2, differential N                                                                                                  |  |  |

| DATA3 P      | Output | MIPI serial data, lane 3, differential P                                                                                                  |  |  |

| DATA3_N      | Output | MIPI serial data, Iane 3, differential N                                                                                                  |  |  |

| DATA4_P      | Output | MIPI serial data, Iane 4, differential P                                                                                                  |  |  |

| DATA4_N      | Output | MIPI serial data, lane 4, differential N                                                                                                  |  |  |

| CLK P        | Output | Output MIPI serial clock, differential P                                                                                                  |  |  |

| CLK_N        | Output | Output MIPI serial clock, differential N                                                                                                  |  |  |

| VDD_HiSPi    | Power  | ·                                                                                                                                         |  |  |

| VDD_HiSPi_TX | Power  | 0.4V-0.8V or 1.7V - 1.9V port to HiSPi Output Driver. Set the High_VCM (R0x306E[9]) bit to 1 when configuring VDD_HiSPi_TX to 1.7 – 1.9V. |  |  |

AR0330: 1/3-Inch CMOS Digital Image Sensor Pin Descriptions

### Table 5: Pin Descriptions (continued)

| Name       | Туре  | Description                                                                                                                                    |

|------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------|

| VAAHV_NPIX | Power | Power supply pin used to program the sensor OTPM (one-time programmable memory). This pin must be connected to ground during normal operation. |

#### Table 6: CSP Package Pin Descriptions

|   | 1      | 2          | 3       | 4       | 5       | 6       | 7            | 8         |

|---|--------|------------|---------|---------|---------|---------|--------------|-----------|

| Α | VAA    | VAAHV_NPIX | AGND    | AGND    | VAA     | VDD     | TEST         | DGND      |

| В | DGND   | NC         | VAA_PIX | DGND    | VDD_IO  | TRIGGER | RESET_BAR    | EXTCLK    |

| С | VDD    | SHUTTER    | DGND    | SLVSC_P | SLVS3_P | SLVS3_N | SLVS2_N      | SLVS2_P   |

| D | SADDR  | Sclk       | SDATA   | FLASH   | SLVSC_N | SLVS1_P | VDD_HiSPi_TX | VDD_HiSPi |

| E | VDD_IO | VDD_IO     | CLK_N   | CLK_P   | DGND    | SLVS1_N | SLVS0_N      | SLVS0_P   |

| F | DGND   | VDD_IO     | DGND    | DGND    | DATA4_P | DATA_N  | DATA_P       | VDD_PLL   |

| G | VDD_IO | VDD        | DGND    | VDD_IO  | DATA4_N | DATA3_N | DATA2_N      | VDD       |

| Н | DGND   | VDD_IO     | VDD_IO  | DGND    | VDD_PLL | DATA3_P | DATA2_P      | VDD_PLL   |

Note: Pins labeled NC (Not Connected) should be left floating.

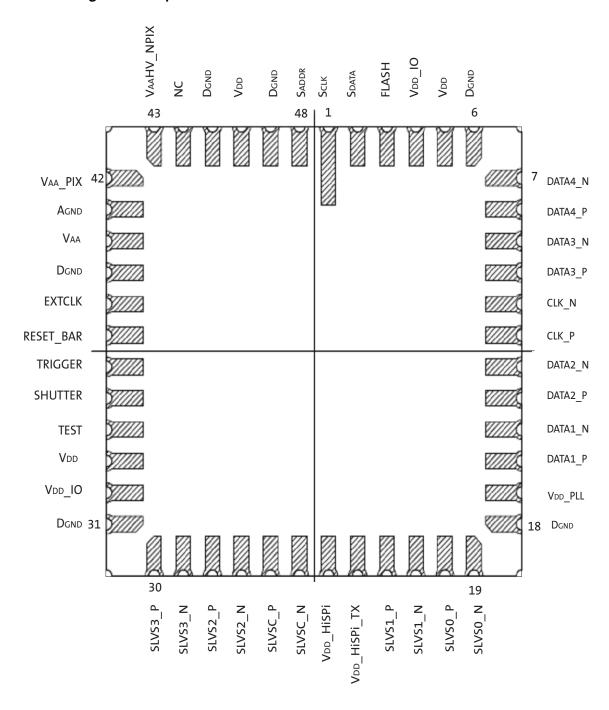

Figure 5: CLCC Package Pin Descriptions

Note: Pins labeled NC (Not Connected) should be left floating.

#### **Sensor Initialization**

#### **Power-Up Sequence**

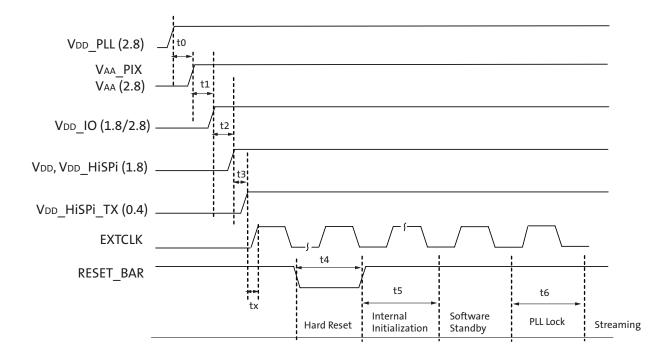

The recommended power-up sequence for the AR0330 is shown in Figure 6. The available power supplies (VDD\_IO, VDD\_HiSPi, VDD\_HiSPi\_TX, VDD\_PLL, VAA, VAA\_PIX) must have the separation specified below.

- 1. Turn on VDD\_PLL power supply.

- 2. After 100µs, turn on VAA and VAA\_PIX power supply.

- 3. After 100µs, turn on VDD\_IO power supply.

- 4. After 100μs, turn on VDD and VDD\_HiSPi power supplies.

- 5. After 100µs, turn on VDD\_HiSPi\_TX power supply.

- 6. After the last power supply is stable, enable EXTCLK.

- 7. Assert RESET BAR for at least 1ms.

- 8. Wait 150000 EXTCLKs (for internal initialization into software standby.

- 9. Configure PLL, output, and image settings to desired values.

- 10. Wait 1ms for the PLL to lock.

- 11. Set streaming mode (R0x301a[2] = 1).

Figure 6: Power Up

AR0330: 1/3-Inch CMOS Digital Image Sensor Sensor Initialization

Table 7: Power-Up Sequence

| Definition                          | Symbol | Minimum        | Typical         | Maximum | Unit    |

|-------------------------------------|--------|----------------|-----------------|---------|---------|

| VDD_PLL to VAA/VAA_PIX <sup>3</sup> | t0     | 0              | 100             | -       | μS      |

| VAA/VAA_PIX to VDD_IO               | t1     | 0              | 100             | -       | μS      |

| VDD_IO to VDD and VDD_HiSPi         | t2     | 10             | 100             | -       | μS      |

| VDD and VDD_HiSPi to VDD_HiSPi_TX   | t3     | 10             | 100             | -       | μS      |

| External clock settling time        | tx     | _              | 30 <sup>1</sup> | _       | mS      |

| Hard Reset                          | t4     | 1 <sup>2</sup> | _               | -       | mS      |

| Internal Initialization             | t5     | 150000         | _               | -       | EXTCLKS |

| PLL Lock Time                       | t6     | 1              | _               | _       | mS      |

- 1. External clock settling time is component-dependent, usually taking about 10 100 mS.

- 2. Hard reset time is the minimum time required after power rails are settled. In a circuit where Hard reset is held down by RC circuit, then the RC time must include the all power rail settle time and Xtal settle time.

- 3. It is critical that VDD\_PLL is not powered up after the other power supplies. It must be powered before or at least at the same time as the others. If the case happens that VDD\_PLL is powered after other supplies then sensor may have functionality issues and will experience high current draw on this supply.

- 4. VDD\_MIPI is tied to VDD\_PLL in both the CLCC and the CSP packagesand must be powered to 2.8V. The VDD\_HiSPi and VDD\_HiSPi\_TX supplies do not need to be turned on if the sensor is configured to use the MIPI or parallel interface.

AR0330: 1/3-Inch CMOS Digital Image Sensor Sensor Initialization

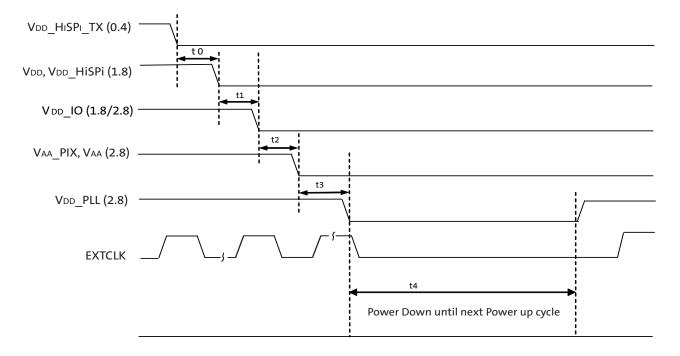

#### **Power-Down Sequence**

The recommended power-down sequence for the AR0330 is shown in Figure 7. The available power supplies (VDD\_IO, VDD\_HiSPi, VDD\_HiSPi\_TX, VDD\_PLL, VAA, VAA\_PIX) must have the separation specified below.

- 1. Disable streaming if output is active by setting standby R0x301a[2] = 0

- 2. The soft standby state is reached after the current row or frame, depending on configuration, has ended.

- 3. Turn off VDD\_HiSPi\_TX.

- 4. Turn off VDD and VDD\_HiSPi.

- 5. Turn off VDD\_IO

- 6. Turn off VAA/VAA\_PIX.

- 7. Turn off VDD\_PLL.

Figure 7: Power Down

Table 8: Power-Down Sequence

| Definition                         | Symbol | Minimum | Typical | Maximum | Unit |

|------------------------------------|--------|---------|---------|---------|------|

| VDD_HiSPi _TX to VDD and VDD_HiSPi | t0     | 0       | _       | _       | μS   |

| Vdd and Vdd_HiSPi to Vdd_IO        | t1     | 0       | -       | _       | μS   |

| VDD_IO to VAA/VAA_PIX              | t2     | 0       | _       | _       | μS   |

| VAA/VAA_PIX to VDD_PLL             | t3     | 0       | _       | _       | μS   |

| PwrDn until Next PwrUp Time        | t4     | 100     | -       | _       | mS   |

t4 is required between power down and next power up time; all decoupling caps from regulators must be completely discharged.

AR0330: 1/3-Inch CMOS Digital Image Sensor Electrical Characteristics

### **Electrical Characteristics**

#### Table 9: DC Electrical Definitions and Characteristics

$^{f} EXTCLK = 24 \text{ MHz}; VDD = 1.8V; VDD\_IO = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; VDD\_HiSPi = 1.8V, VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60 fps = 1.8V; VDD\_HiSPi\_TX = 0.4V; Output load = 68.5pF; T_J = 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; DLL set to 0; 2304x1296 at 60°C; Data Rate = 588 Mbps; Data$

| Definition                          | Condition                     | Symbol       | Min | Тур | Max | Unit |

|-------------------------------------|-------------------------------|--------------|-----|-----|-----|------|

| Core digital voltage                |                               | VDD          | 1.7 | 1.8 | 1.9 | V    |

| I/O digital voltage                 | Parallel pixel data interface | VDD_IO       | 1.7 | 1.8 | 1.9 | V    |

| Analog voltage                      |                               | VAA          | 2.4 | 2.8 | 3.1 | V    |

| Pixel supply voltage                |                               | VAA_PIX      | 2.4 | 2.8 | 3.1 | V    |

| PLL supply voltage                  |                               | VDD_PLL      | 2.4 | 2.8 | 3.1 | V    |

| HiSPi digital voltage               |                               | Vdd_HiSPi    | 1.7 | 1.8 | 1.9 | V    |

| HiSPi I/O digital voltage           |                               | VDD_HiSPi_TX | 0.3 | 0.4 | 0.9 | V    |

| Digital operating current           |                               |              |     | TBD |     | mA   |

| I/O digital operating current       |                               |              |     | TBD |     | mA   |

| Analog operating current            |                               |              |     | TBD |     | mA   |

| Pixel supply current                |                               |              |     | TBD |     | mA   |

| PLL supply current                  |                               |              |     | TBD |     | mA   |

| HiSPi digital operating current     |                               |              |     | TBD |     | mA   |

| HiSPi I/O digital operating current |                               |              |     | TBD |     | mA   |

| Soft standby (clock on)             |                               |              |     | TBD |     | mW   |

Caution

Stresses greater than those listed in Table 10 may cause permanent damage to the device. This is a stress rating only, and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

Table 10: Absolute Maximum Ratings

| Symbol           | Definition                | Condition | Min  | Max | Unit |

|------------------|---------------------------|-----------|------|-----|------|

| VDD_MAX          | Core digital voltage      |           | -0.3 | 2.4 | V    |

| VDD_IO_MAX       | I/O digital voltage       |           | -0.3 | 4   | V    |

| VAA_MAX          | Analog voltage            |           | -0.3 | 4   | V    |

| VAA_PIX          | Pixel supply voltage      |           | -0.3 | 4   | V    |

| VDD_PLL          | PLL supply voltage        |           | -0.3 | 4   | V    |

| VDD_HiSPi_MAX    | HiSPi digital voltage     |           | -0.3 | 2.4 | V    |

| VDD_HiSPi_TX_MAX | HiSPi I/O digital voltage |           | -0.3 | 2.4 | V    |

| t <sub>ST</sub>  | Storage temperature       |           | -40  | 85  | °C   |

Note: Exposure to absolute maximum rating conditions for extended periods may affect reliability.

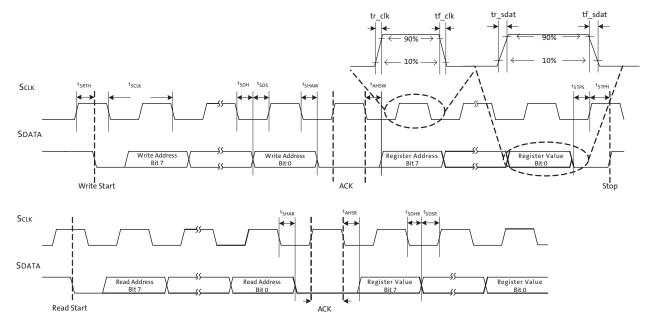

Figure 8: Two-Wire Serial Bus Timing Parameters

Note: Read sequence: For an 8-bit READ, read waveforms start after WRITE command and register address are issued.

Table 11: Two-Wire Serial Register Interface Electrical Characteristics

fEXTCLK = 24 MHz; VDD = 1.8V; VDD\_IO = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF; T<sub>J</sub> = 60°C

| Symbol | Parameter             | Condition                                    | Min   | Тур   | Max          | Unit |

|--------|-----------------------|----------------------------------------------|-------|-------|--------------|------|

| VIL    | Input LOW voltage     |                                              | -0.5  | 0.73  | 0.3 x VDD_IO | V    |

| lin    | Input leakage current | No pull up resistor;<br>Vin = VDD_IO or DGND | -2    |       | 2            | μΑ   |

| Vol    | Output LOW voltage    | At specified 2mA                             | 0.031 | 0.032 | 0.035        | V    |

| lol    | Output LOW current    | At specified Vol 0.1V                        |       |       | 3            | mA   |

| CIN    | Input pad capacitance |                                              |       |       | 6            | pF   |

| Cload  | Load capacitance      |                                              |       |       |              | pF   |

Table 12: Two-Wire Serial Register Interface Timing Specification

fEXTCLK = 24 MHz; VDD = 1.8V; VDD IO = 1.8V; VAA = 2.8V; VAA PIX = 2.8V; VDD PLL = 2.8V; Output load = 68.5pF; T<sub>1</sub> = 60°C

| Symbol            | Parameter                    | Condition             | Min  | Тур | Max  | Unit |

|-------------------|------------------------------|-----------------------|------|-----|------|------|

| <sup>f</sup> SCLK | Serial interface input clock | _                     | 0    | 100 | 400  | kHz  |

|                   | SCLK duty cycle              | Vod                   | 45   | 50  | 60   | %    |

| <sup>t</sup> R    | SCLK/SDATA rise time         |                       |      |     | 300  | μs   |

| <sup>t</sup> SRTS | Start setup time             | Master WRITE to slave | 0.6  |     |      | μs   |

| <sup>t</sup> SRTH | Start hold time              | Master WRITE to slave | 0.4  |     |      | μs   |

| <sup>t</sup> SDH  | SDATA hold                   | Master WRITE to slave | 0.3  |     | 0.65 | μs   |

| <sup>t</sup> SDS  | SDATA setup                  | Master WRITE to slave | 0.3  |     |      | μs   |

| <sup>t</sup> SHAW | SDATA hold to ACK            | Master READ to slave  | 0.15 |     | 0.65 | μs   |

| <sup>t</sup> AHSW | ACK hold to SDATA            | Master WRITE to slave | 0.15 |     | 0.70 | μs   |

| <sup>t</sup> STPS | Stop setup time              | Master WRITE to slave | 0.3  |     |      | μs   |

AR0330: 1/3-Inch CMOS Digital Image Sensor Electrical Characteristics

Table 12: Two-Wire Serial Register Interface Timing Specification

<sup>f</sup>EXTCLK = 24 MHz; VDD = 1.8V; VDD\_IO = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF; T<sub>J</sub> = 60°C

| Symbol            | Parameter         | Condition              | Min  | Тур | Max  | Unit |

|-------------------|-------------------|------------------------|------|-----|------|------|

| <sup>t</sup> STPH | Stop hold time    | Master WRITE to slave  | 0.6  |     |      | μs   |

| <sup>t</sup> SHAR | SDATA hold to ACK | Master WRITE to slave  | 0.3  |     | 1.65 | μs   |

| <sup>t</sup> AHSR | ACK hold to SDATA | Master WRITE to slave  | 0.3  |     | 0.65 | μs   |

| <sup>t</sup> SDHR | SDATA hold        | Master READ from slave | .012 |     | 0.70 | μs   |

| <sup>t</sup> SDSR | SDATA setup       | Master READ from slave | 0.3  |     |      | μs   |

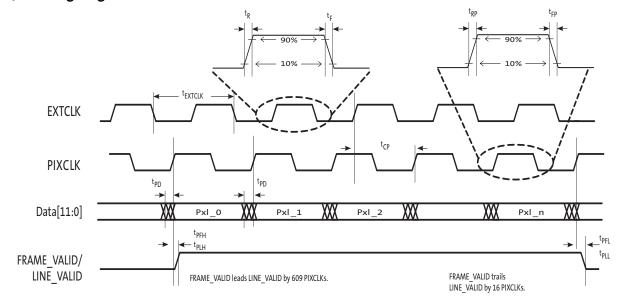

Figure 9: I/O Timing Diagram

\*PLL disabled for <sup>t</sup>CP

Table 13: I/O Parameters

$^{f}$ EXTCLK = 24 MHz; VDD = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF;  $T_{J}$  = 60°C; CLK\_OP = 98 MPixel/s

| Symbol | Definition                       | Conditions                             | Min           | Max          | Units |

|--------|----------------------------------|----------------------------------------|---------------|--------------|-------|

| VIH    | Input HIGH voltage               | VDD_IO = 1.8V                          | 1.4           | VDD_IO + 0.3 |       |

|        |                                  | VDD_IO = 2.8V                          | 2.4           |              |       |

| VIL    | Input LOW voltage                | VDD_IO = 1.8V                          | GND - 0.3     | 0.4          | V     |

|        |                                  | VDD_IO = 2.8V                          | GND - 0.3     | 0.8          |       |

| lin    | Input leakage current            | No pull-up resistor; VIN = VDD OR DGND | -20           | 20           | μА    |

| Vон    | Output HIGH voltage              | At specified IOH                       | VDD_IO - 0.4V | -            | V     |

| Vol    | Output LOW voltage               | At specified IOL                       | _             | 0.4          | V     |

| Іон    | Output HIGH current              | At specified Voн                       | _             | -12          | mA    |

| lor    | Output LOW current               | At specified VOL                       | _             | 9            | mA    |

| loz    | Tri-state output leakage current |                                        | -             | 10           | μА    |

AR0330: 1/3-Inch CMOS Digital Image Sensor Electrical Characteristics

#### Table 14: I/O Timing

<sup>f</sup>EXTCLK = 24 MHz; VDD = 1.8V; VDD\_IO = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF; T<sub>I</sub> = 60°C; CLK\_OP = 98 MPixel/s

| Symbol              | Definition                 | Conditions   | Min | Тур | Max | Units |

|---------------------|----------------------------|--------------|-----|-----|-----|-------|

| fextclk             | Input clock frequency      | PLL enabled  | 2   | 24  | 64  | MHz   |

| <sup>t</sup> EXTCLK | Input clock period         | PLL enabled  | 166 | 41  | 20  | ns    |

| <sup>t</sup> R      | Input clock rise time      |              | 0.1 | _   | 1   | V/ns  |

| <sup>t</sup> F      | Input clock fall time      |              | 0.1 | _   | 1   | V/ns  |

|                     | Clock duty cycle           |              | 45  | 50  | 55  | %     |

| <sup>t</sup> JITTER | Input clock jitter         |              | _   | _   | 0.3 | ns    |

| Output pin slew     | Fastest                    | CLOAD = 15pF | _   | 0.7 | _   | V/ns  |

| <sup>f</sup> PIXCLK | PIXCLK frequency           | Default      | _   | 80  | _   | MHz   |

| <sup>t</sup> PD     | PIXCLK to data valid       | Default      | _   | -   | 3   | ns    |

| <sup>t</sup> PFH    | PIXCLK to FRAME_VALID HIGH | Default      | _   | -   | 3   | ns    |

| <sup>t</sup> PLH    | PIXCLK to LINE_VALID HIGH  | Default      | _   | -   | 3   | ns    |

| <sup>t</sup> PFL    | PIXCLK to FRAME_VALID LOW  | Default      | -   | -   | 3   | ns    |

| <sup>t</sup> PLL    | PIXCLK to LINE_VALID LOW   | Default      | _   | _   | 3   | ns    |

#### Table 15: Parallel I/O Rise Slew Rate

$^{f}$ EXTCLK = 24 MHz; VDD = 1.8V; VAA = 2.8V; VAA\_PIX = 2.8V; VDD\_PLL = 2.8V; Output load = 68.5pF;  $T_{J}$  = 60°C; CLK\_OP = 98 MPixel/s

|        |       | Parallel Slew Rate (R0x306E[15:13]) |       |       |       |       |       |       |       |

|--------|-------|-------------------------------------|-------|-------|-------|-------|-------|-------|-------|

| VDD_IO | 0     | 1                                   | 2     | 3     | 4     | 5     | 6     | 7     | Units |

| 1.70V  | 0.069 | 0.115                               | 0.172 | 0.239 | 0.325 | 0.43  | 0.558 | 0.836 | V/ns  |

| 1.80V  | 0.078 | 0.131                               | 0.195 | 0.276 | 0.375 | 0.507 | 0.667 | 1.018 |       |

| 1.95V  | 0.093 | 0.156                               | 0.233 | 0.331 | 0.456 | 0.62  | 0.839 | 1.283 |       |

| 2.50V  | 0.15  | 0.252                               | 0.377 | 0.539 | 0.759 | 1.07  | 1.531 | 2.666 |       |

| 2.80V  | 0.181 | 0.305                               | 0.458 | 0.659 | 0.936 | 1.347 | 1.917 | 3.497 |       |

| 3.10V  | 0.212 | 0.361                               | 0.543 | 0.78  | 1.114 | 1.618 | 2.349 | 4.14  |       |

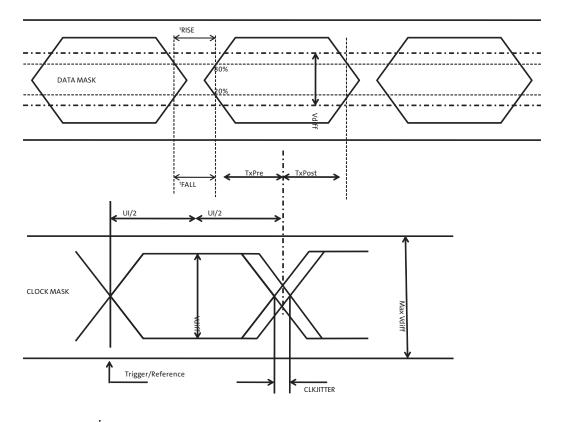

Figure 10: HiSPi Eye Diagram for Both Clock and Data Signals

Table 16: HiSPi Rise and Fall Times at 660 Mbps

Measurement Conditions: VDD\_HiSPi = 1.8V, VDD\_HiSPi\_TX = 0.8V; Data Rate = 660 Mbps; DLL set to 0

| Parameter                       | Name              | Value | Unit |

|---------------------------------|-------------------|-------|------|

| Max Setup Time from Transmitter | TxPRE             | 0.44  | UI   |

| Max Hold Time from Transmitter  | TxPost            | 0.44  | UI   |

| Rise time t                     | <sup>t</sup> RISE | 350   | ps   |

| Fall time t                     | <sup>t</sup> FALL | 350   | ps   |

| Output impedance                |                   | 66    | Ω    |

Table 17: HiSPi Rise and Fall Times at 360 MHz

Measurement Conditions: VDD\_HiSPi = 1.8V;VDD\_HiSPi\_TX = 0.8V; Data Rate = 360 Mbps; DLL set to 0 DLL set to 0

| Parameter                       | Name              | Value | Unit |

|---------------------------------|-------------------|-------|------|

| Max Setup Time from Transmitter | TxPRE             | 0.48  | UI   |

| Max Hold Time from Transmitter  | TxPost            | 0.42  | UI   |

| Rise time t                     | <sup>t</sup> RISE | 350   | ps   |

| Fall time t                     | <sup>t</sup> FALL | 350   | ps   |

| Output impedance                |                   | 66    | Ω    |

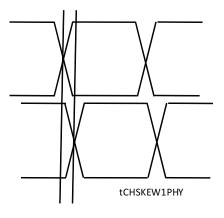

Figure 11: HiSPi Skew Between Data Signals Within the PHY

Table 18: Channel, PHY and Intra-PHY Skew

Measurement Conditions: VDD\_HiSPi = 1.8V;VDD\_HiSPi\_TX = 0.8V; Data Rate =480 Mbps; DLL set to 0

| Data Lane Skew in Reference to Clock | tCHSKEW1PHY | -150 | ps |

|--------------------------------------|-------------|------|----|

|--------------------------------------|-------------|------|----|

Table 19: Clock DLL Steps

Measurement Conditions: VDD\_HiSPi = 1.8V;VDD\_HiSPi\_TX = 0.8V; Data DLL set to 0

| Clock DLL Step          | 1    | 2     | 3    | 4     | 5    | Step |

|-------------------------|------|-------|------|-------|------|------|

| Delay at 660 Mbps       | 0.25 | 0.375 | 0.5  | 0.625 | 0.75 | UI   |

| Eye_opening at 660 Mbps | 0.85 | 0.78  | 0.71 | 0.71  | 0.69 | UI   |

| Eye_opening at 360 MHz  | 0.89 | 0.83  | 0.81 | 0.60  | 046  | IJ   |

Note: The Clock DLL Steps 6 and 7 are not recommended by Aptina for the AR0330 Rev. 1.

Table 20: Data DLL Steps

Measurement Conditions: VDD\_HiSPi = 1.8V;VDD\_HiSPi\_TX = 0.8V; Clock DLL set to 0

| Data DLL Step           | 1    | 2     | 4     | 6     | Step |

|-------------------------|------|-------|-------|-------|------|

| Delay at 660 Mbps       | 0.25 | 0.375 | 0.625 | 0.875 | UI   |

| Eye opening at 660 Mbps | 0.79 | 0.84  | 0.71  | 0.61  | UI   |

| Eye opening at 360 MHz  | 0.85 | 0.83  | 0.82  | 0.77  | UI   |

Note: The Data DLL Steps 3, 5, and 7 are not recommended by Aptina for the AR0330 Rev. 1.

AR0330: 1/3-Inch CMOS Digital Image Sensor Sequencer

### Sequencer

The sequencer digital block determines the order and timing of operations required to sample pixel data from the array. During sensor initialization, the sequencer will be programmed into memory from the sensor OTPM (One Time Programmable Memory). The OTPM is configured during production.

The sequencer digital block can be reprogrammed using the following instructions:

Program a new sequencer.

- 1. Place the sensor in standby.

- 2. Write 0x8000 to R0x3088 ("seq\_ctrl\_port").

- 3. Write each instruction incrementally to R0x3086. Each write must be 16-bit consisting of two bytes {Byte[N], Byte[N+1]}.

- 4. If the sequencer consists of an odd number of bytes, set the last byte to "0".

Read the instructions stored in the sequencer.

- 1. Place the sensor in standby.

- 2. Write 0xC000 to R0x3088 ("seq\_ctrl\_port").

- 3. Sequentially read 2-bytes at a time from R0x3086.

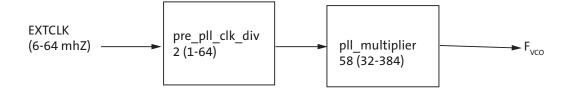

#### **Sensor PLL**

#### VCO

#### Figure 12: Relationship Between Readout Clock and Peak Pixel Rate

The sensor contains a phase-locked loop (PLL) that is used for timing generation and control. The required VCO clock frequency is attained through the use of a pre-PLL clock divider followed by a multiplier. The multiplier is followed by set of dividers used to generate the output clocks required for the sensor array, the pixel analog and digital readout paths, and the output parallel and serial interfaces.

#### **Dual Readout Paths**

There are two readout paths within the sensor digital block. The sensor PLL should be configured so that the total pixel rate across both readout paths equals the total pixel Relationship Between Sensor Clock Configuration and Peak Pixel Rate

Figure 13: Sensor Dual Readout Paths

The sensor row timing calculations refers to each data-path individually. For example, the sensor default configuration uses 1248 clocks per row (line\_length\_pck) to output 2304 active pixels per row. The aggregate clocks per row seen by the receiver will be 2496 clocks (1248 x 2 readout paths).

### **Parallel PLL Configuration**

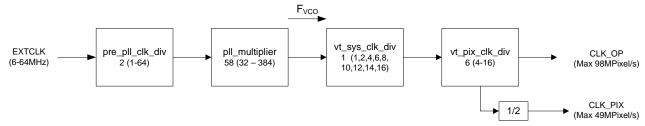

Figure 14: PLL for the Parallel Interface

The parallel interface has a maximum output data-rate of 98MPixel/s.

The maximum output of the parallel interface is 98 MPixel/s (CLK\_OP). This will limit the readout clock (CLK\_PIX) to 49 MPixel/s. The sensor will not use the  $F_{SERIAL}$ ,  $F_{SERIAL}$ , or CLK\_OP when configured to use the parallel interface.

Table 21: PLL Parameters for the Parallel Interface

| Parameter      | Symbol           | Min | Max | Unit     |

|----------------|------------------|-----|-----|----------|

| External Clock | EXTCLK           | 6   | 64  | MHz      |

| VCO Clock      | F <sub>VCO</sub> | 384 | 768 | MHz      |

| Readout Clock  | CLK_PIX          |     | 49  | Mpixel/s |

| Output Clock   | CLK_OP           |     | 98  | Mpixel/s |

Table 22: Example PLL Configuration for the Parallel Interface

| Parameter         | Value | Output                      |  |

|-------------------|-------|-----------------------------|--|

| F <sub>VCO</sub>  |       | 588 MHz (Max)               |  |

| vt_sys_clk_div    | 1     |                             |  |

| vt_pix_clk_div    | 6     |                             |  |

| CLK_PIX           |       | 49 MPixel/s (= 588MHz / 12) |  |

| CLK_OP            |       | 98 MPixel/s (= 588MHz / 6)  |  |

| Output pixel rate |       | 98 MPixel/s                 |  |

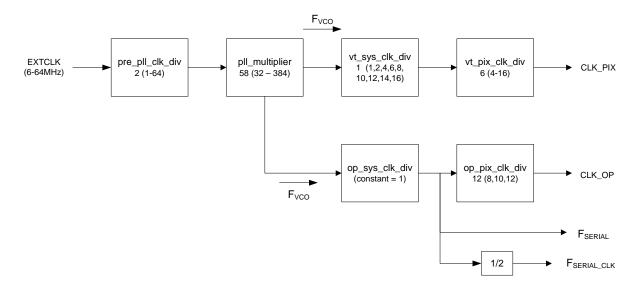

#### **Serial PLL Configuration**

Figure 15: PLL for the Serial Interface

The sensor will use op\_sys\_clk\_div and op\_pix\_clk\_div to configure the output clock per lane (CLK\_OP). The configuration will depend on the number of active lanes (1, 2, or 4) configured. To configure the sensor protocol and number of lanes, refer to "Serial Configuration" on page 31.

Table 23: PLL Parameters for the Serial Interface

| Parameter                          | Symbol                  | Min                       | Max                       | Unit     |

|------------------------------------|-------------------------|---------------------------|---------------------------|----------|

| External Clock                     | EXTCLK                  | 6                         | 64                        | MHz      |

| VCO Clock                          | F <sub>VCO</sub>        | 384                       | 768                       | MHz      |

| Readout Clock                      | CLK_PIX                 |                           | 98                        | Mpixel/s |

| Output Clock                       | CLK_OP                  |                           | 49                        | Mpixel/s |

| Output Serial Data Rate Per Lane   | F <sub>SERIAL</sub>     | 300 (HiSPi)<br>384 (MIPI) | 700 (HiSPi)<br>768 (MIPI) | Mbps     |

| Output Serial Clock Speed Per Lane | F <sub>SERIAL_CLK</sub> | 150 (HiSPi)<br>192 (MIPI) | 350(HiSPi)<br>384 (MIPI)  | MHz      |

The serial output should be configured so that it adheres to the following rules:

AR0330: 1/3-Inch CMOS Digital Image Sensor Sensor PLL

- The maximum data-rate per lane ( $F_{SERIAL}$ ) is 768Mbps/lane (MIPI) and 700Mbps/lane (HiSPi).

- The output pixel rate per lane (CLK\_OP) should be configured so that the sensor output pixel rate matches the peak pixel rate (2 x CLK\_PIX).

- 4-lane: 4 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 196 Mpixel/s)

- 2-lane: 2 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 98 Mpixel/s)

- 1-lane: 1 x CLK\_OP = 2 x CLK\_PIX = Pixel Rate (max: 76 Mpixel/s)

Table 24: Example PLL Configurations for the Serial Interface

|                         | 4-lane |        | 2-lane |        | 1-lane |        | Notes |          |

|-------------------------|--------|--------|--------|--------|--------|--------|-------|----------|

| Parameter               | 12-bit | 10-bit | 12-bit | 10-bit | 12-bit | 10-bit | 8-bit | Notes    |

| F <sub>VCO</sub>        | 588    | 490    | 588    | 490    | 768    | 768    | 768   | MHz      |

| vt_sys_clk_div          | 1      | 1      | 2      | 2      | 4      | 4      | 4     |          |

| vt_pix_clk_div          | 6      | 5      | 6      | 5      | 6      | 5      | 4     |          |

| op_sys_clk_div          | 1      | 1      | 1      | 1      | 1      | 1      | 1     |          |

| op_pix_clk_div          | 12     | 10     | 12     | 10     | 12     | 10     | 8     |          |

| F <sub>SERIAL</sub>     | 588    | 490    | 588    | 490    | 768    | 768    | 768   | MHz      |

| F <sub>SERIAL_CLK</sub> | 294    | 245    | 294    | 245    | 384    | 384    | 384   | MHz      |

| CLK_PIX                 | 98     | 98     | 49     | 49     | 64     | 76.8   | 96    | Mpixel/s |

| CLK_OP                  | 49     | 49     | 49     | 49     | 64     | 76.8   | 96    | Mpixel/s |

| Pixel Rate              | 196    | 196    | 98     | 98     | 64     | 76.8   | 96    | Mpixel/s |

### **Pixel Output Interfaces**

#### **Parallel Interface**

The parallel pixel data interface uses these output-only signals:

- FV

- LV

- PIXCLK

- DOUT[11:0]

The parallel pixel data interface is disabled by default at power up and after reset. It can be enabled by programming R0x301A. Table 26 on page 27 shows the recommended settings.

When the parallel pixel data interface is in use, the serial data output signals can be left unconnected. Set reset\_register[12] to disable the serializer while in parallel output mode.

#### **Output Enable Control**

When the parallel pixel data interface is enabled, its signals can be switched asynchronously between the driven and High-Z under pin or register control, as shown in Table 25.

**Table 25:** Output Enable Control

| OE_BAR Pin | Drive Signals R0x301A-B[6] | Description      |

|------------|----------------------------|------------------|

| Disabled   | 0                          | Interface High-Z |

| Disabled   | 1                          | Interface driven |

| 1          | 0                          | Interface High-Z |

| Х          | 1                          | Interface driven |

| 0          | X                          | Interface driven |

#### **Configuration of the Pixel Data Interface**

Fields in R0x301A are used to configure the operation of the pixel data interface. The supported combinations are shown in Table 26.

Table 26: Configuration of the Pixel Data Interface

| Serializer<br>Disable<br>R0x301<br>A-B[12] | Parallel<br>Enable<br>R0x301A–B[7] | Standby<br>End-of-Frame<br>R0x301A–B[4] | Description                                                                                                                                                                                                                                         |

|--------------------------------------------|------------------------------------|-----------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0                                          | 0                                  | 1                                       | Power up default. Serial pixel data interface and its clocks are enabled. Transitions to soft standby are synchronized to the end of frames on the serial pixel data interface.                                                                     |

| 1                                          | 1                                  | 0                                       | Parallel pixel data interface, sensor core data output. Serial pixel data interface and its clocks disabled to save power. Transitions to soft standby are synchronized to the end of the current row readout on the parallel pixel data interface. |

| 1                                          | 1                                  | 1                                       | Parallel pixel data interface, sensor core data output. Serial pixel data interface and its clocks disabled to save power. Transitions to soft standby are synchronized to the end of frames in the parallel pixel data interface.                  |

#### **High Speed Serial Pixel Data Interface**

The High Speed Serial Pixel (HiSPi) interface uses four data and one clock low voltage differential signaling (LVDS) outputs.

- SLVSC P

- SLVSC N

- SLVS0 P

- SLVS0\_N

- SLVS1\_P

- SLVS1\_N

- SLVS2\_P

- SLVS2\_N

- SLVS3\_P

- SLVS3 N

The HiSPi interface supports three protocols, Streaming S, Streaming SP, and Packetized SP. The streaming protocols conform to a standard video application where each line of active or intra-frame blanking provided by the sensor is transmitted at the same length. The Packetized SP protocol will transmit only the active data ignoring line-to-line and frame-to-frame blanking data.

These protocols are further described in the High-Speed Serial Pixel (HiSPi<sup>TM</sup>) Interface Protocol Specification V1.00.00.

The HiSPi interface building block is a unidirectional differential serial interface with four data and one double data rate (DDR) clock lanes. One clock for every four serial data lanes is provided for phase alignment across multiple lanes. Figure 16 shows the configuration between the HiSPi transmitter and the receiver.

Figure 16: HiSPi Transmitter and Receiver Interface Block Diagram

#### **HiSPi Physical Layer**

The HiSPi physical layer is partitioned into blocks of four data lanes and an associated clock lane. Any reference to the PHY in the remainder of this document is referring to this minimum building block.

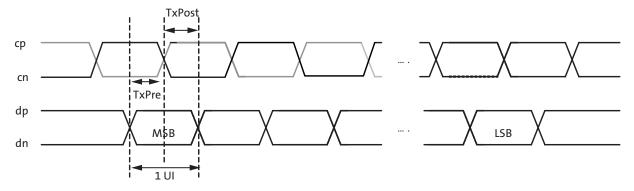

The PHY will serialize a 10-, 12-, 14- or 16-bit data word and transmit each bit of data centered on a rising edge of the clock, the second on the falling edge of clock. Figure 17 shows bit transmission. In this example, the word is transmitted in order of MSB to LSB. The receiver latches data at the rising and falling edge of the clock.

Figure 17: Timing Diagram

#### **DLL Timing Adjustment**

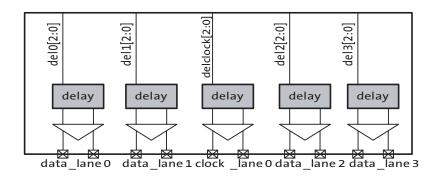

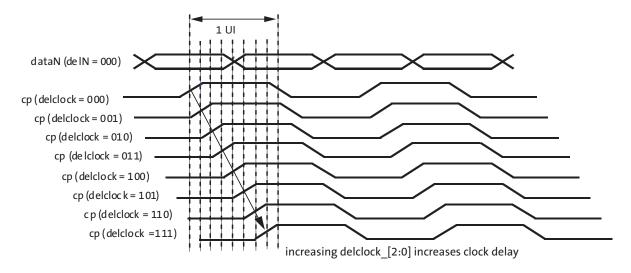

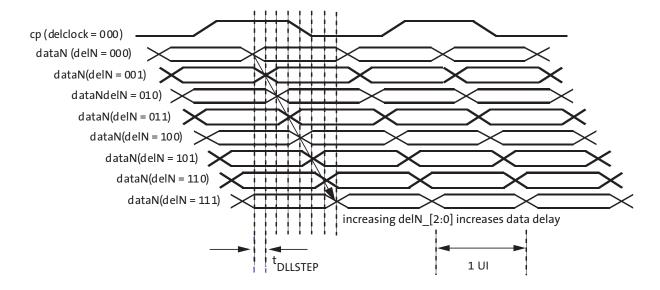

The specification includes a DLL to compensate for differences in group delay for each data lane. The DLL is connected to the clock lane and each data lane, which acts as a control master for the output delay buffers. Once the DLL has gained phase lock, each lane can be delayed in 1/8 unit interval (UI) steps. This additional delay allows the user to increase the setup or hold time at the receiver circuits and can be used to compensate for skew introduced in PCB design.

If the DLL timing adjustment is not required, the data and clock lane delay settings should be set to a default code of 0x000 to reduce jitter, skew, and power dissipation.

Figure 18: Block Diagram of DLL Timing Adjustment

Figure 19: Delaying the clock\_lane with Respect to data\_lane

Figure 20: Delaying data\_lane with Respect to the clock\_lane

#### **HiSPi Streaming Mode Protocol Layer**

The HiSPi protocol is described HiSPi Protocol V1.00.00 A.

#### **MIPI Interface**

The serial pixel data interface uses the following output-only signal pairs:

- DATA1\_P

- DATA1 N

- DATA2\_P

- DATA2\_N

- DATA3\_P

- DATA3 N

- DATA4 P

- DATA4 N

- CLK P

- CLK N

The signal pairs use both single-ended and differential signaling, in accordance with the the MIPI Alliance Specification for D-PHY v1.00.00. The serial pixel data interface is enabled by default at power up and after reset.

The DATA0\_P, DATA0\_N, DATA1\_P, DATA1\_N, CLK\_P and CLK\_N pads are set to the Ultra Low Power State (ULPS) if the serial disable bit is asserted (R0x301A-B[12]=1) or when the sensor is in the hardware standby or soft standby system states.

When the serial pixel data interface is used, the LINE\_VALID, FRAME\_VALID, PIXCLK and dout[11:0] signals (if present) can be left unconnected.

### **Serial Configuration**

The serial format should be configured using R0x31AC. This register should be programmed to 0x0C0C when using the parallel interface.

The R0x0112-3 register can be programmed to any of the following data format settings that are supported:

- 0x0C0C Sensor supports RAW12 uncompressed data format

- 0x0C0A The sensor supports RAW12 compressed format (10-bit words) using 12-10 bit A-LAW Compression. See "Compression" on page 49.

- 0x0A0A Sensor supports RAW10 uncompressed data format. This mode is supported by discarding all but the upper 10 bits of a pixel value.

- 0x0808 Sensor supports RAW8 uncompressed data format. This mode is supported by discarding all but the upper 8 bits of a pixel value (MIPI only).

The serial\_format register (R0x31AE) register controls which serial interface is in use when the serial interface is enabled (reset\_register[12] = 0). The following serial formats are supported:

- 0x0201 Sensor supports single-lane MIPI operation

- 0x0202 Sensor supports dual-lane MIPI operation

- 0x0204 Sensor supports quad-lane MIPI operation

- 0x0304 Sensor supports quad-lane HiSPi operation

The MIPI timing registers must be configured differently for 10-bit or 12-bit modes. These modes should be configured when the sensor streaming is disabled. See Table 27 on page 32

| Table 27:  | <b>Recommended MIPI Timing Configuration</b> |

|------------|----------------------------------------------|

| I UDIC 27. | Recommended Will I minning comingulation     |

|          | Confi               |                      |                    |

|----------|---------------------|----------------------|--------------------|

| Register | 10bit, 490Mbps/lane | 12-bit, 588Mbps/lane |                    |

|          | Clocking:           | Clocking: Continuous |                    |

| 0x31B0   | 40                  | 36                   | Frame Preamble     |

| 0x31B2   | 14                  | 12                   | Line Preamble      |

| 0x31B4   | 0x2743              | 0x2643               | MIPI Timing 0      |

| 0x31B6   | 0x114E              | 0x114E               | MIPI Timing 1      |

| 0x31B8   | 0x2049              | 0x2048               | MIPI Timing 2      |

| 0x31BA   | 0x0186              | 0x0186               | MIPI Timing 3      |

| 0x31BC   | 0x8005              | 0x8005               | MIPI Timing 4      |

| 0x31BE   | 0x2003              | 0x2003               | MIPI Config Status |

### **Pixel Sensitivity**

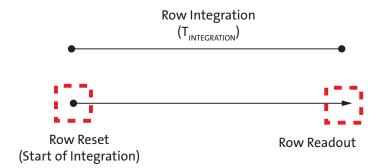

Figure 21: Integration Control in ERS Readout

A pixel's integration time is defined by the number of clock periods between a row's reset and read operation. Both the read followed by the reset operations occur within a row period  $(T_{ROW})$  where the read and reset may be applied to different rows. The read and reset operations will be applied to the rows of the pixel array in a consecutive order.

The integration time in an ERS frame is defined as  $T_{INTEGRATION} = T_{COARSE} - T_{FINE}$ .

The coarse integration time is defined by the number of row periods  $(T_{ROW})$  between a row's reset and the row read. The row period is the defined as the time between row read operations (see Sensor Frame Rate).

$$T_{COARSE} = T_{ROW}^*$$

coarse\_integration\_time (EQ 1)

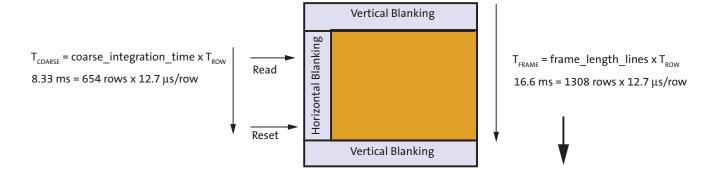

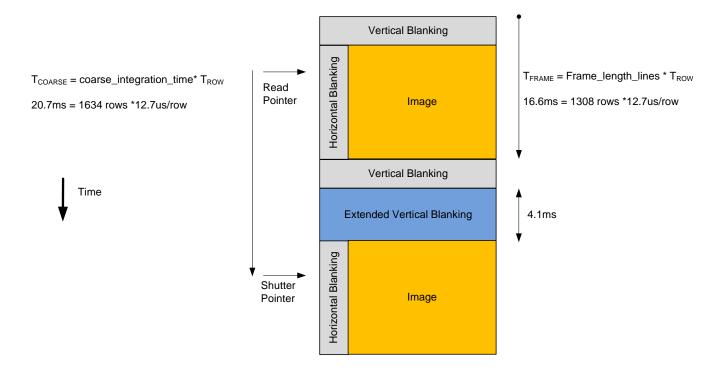

Figure 22: Example of 8.33ms Integration in 16.6ms Frame

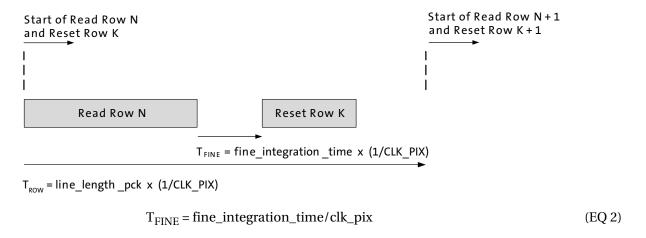

The fine integration is then defined by the number of pixel clock periods between the row reset and row read operation within  $T_{ROW}$ . This period is defined by the  $fine\_integration\_time$  register.

Figure 23: Row Read and Row Reset Showing Fine Integration

The maximum allowed value for fine\_integration\_time is *line\_length\_pck* - 920.

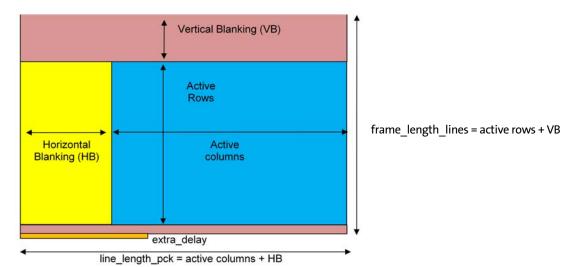

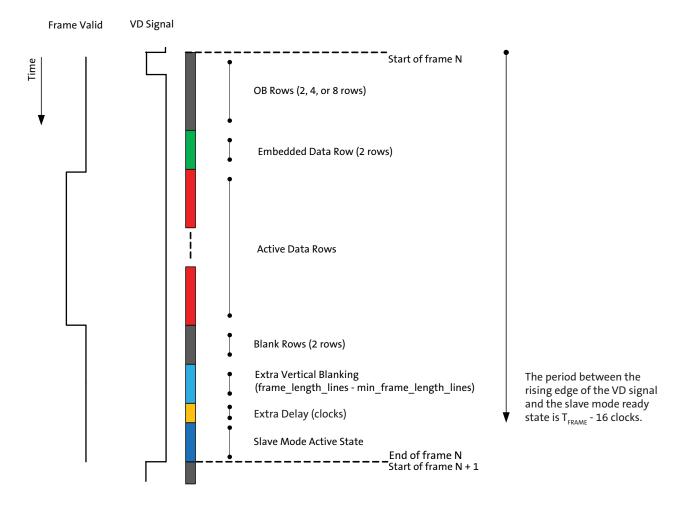

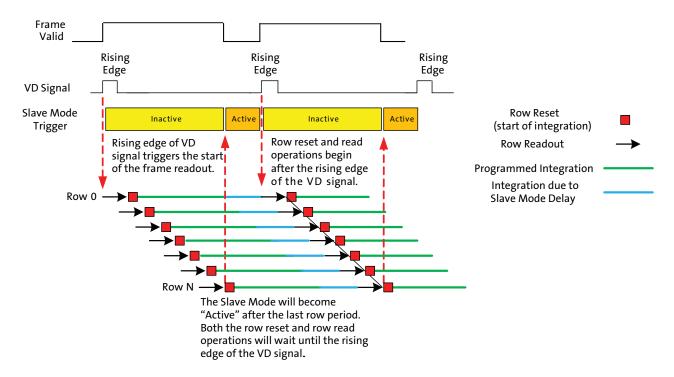

Figure 24: The Row Integration Time is Greater Than the Frame Readout Time